MOSFET

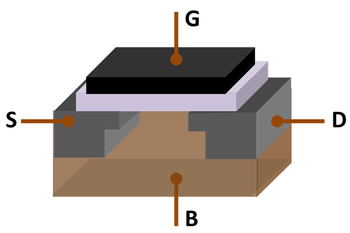

The metal–oxide–semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), also known as the metal–oxide–silicon transistor (MOS transistor, or MOS),[1] is a type of insulated-gate field-effect transistor that is fabricated by the controlled oxidation of a semiconductor, typically silicon. The voltage of the covered gate determines the electrical conductivity of the device; this ability to change conductivity with the amount of applied voltage can be used for amplifying or switching electronic signals.

The MOSFET was invented by Mohamed M. Atalla and Dawon Kahng at Bell Labs in 1959, and first presented in June 1960. It is the basic building block of modern electronics, and the most frequently manufactured device in history, with an estimated total of 13 sextillion (1.3×1022) MOSFETs manufactured between 1960 and 2018.[2] It is the dominant semiconductor device in digital and analog integrated circuits (ICs),[3] and the most common power device.[4] It is a compact transistor that has been miniaturised and mass-produced for a wide range of applications, revolutionizing the electronics industry and the world economy, and being central to the digital revolution, silicon age and information age. MOSFET scaling and miniaturization has been driving the rapid exponential growth of electronic semiconductor technology since the 1960s, and enables high-density ICs such as memory chips and microprocessors. The MOSFET is considered the "workhorse" of the electronics industry.

A key advantage of a MOSFET is that it requires almost no input current to control the load current, when compared with bipolar junction transistors (BJTs). In an enhancement mode MOSFET, voltage applied to the gate terminal can increase the conductivity from the "normally off" state. In a depletion mode MOSFET, voltage applied at the gate can reduce the conductivity from the "normally on" state.[5] MOSFETs are also capable of high scalability, with increasing miniaturization, and can be easily scaled down to smaller dimensions. They also have faster switching speed (ideal for digital signals), much smaller size, consume significantly less power, and allow much higher density (ideal for large-scale integration), compared to BJTs. MOSFETs are also cheaper and have relatively simple processing steps, resulting in high manufacturing yield.

MOSFETs can either be manufactured as part of MOS integrated circuit chips or as discrete MOSFET devices (such as a power MOSFET), and can take the form of single-gate or multi-gate transistors. Since MOSFETs can be made with either p-type or n-type semiconductors (PMOS or NMOS logic, respectively), complementary pairs of MOSFETs can be used to make switching circuits with very low power consumption: CMOS (Complementary MOS) logic.

The name "metal–oxide–semiconductor" (MOS) typically refers to a metal gate, oxide insulation, and semiconductor (typically silicon).[1] However, the "metal" in the name MOSFET is sometimes a misnomer, because the gate material can also be a layer of polysilicon (polycrystalline silicon). Along with oxide, different dielectric materials can also be used with the aim of obtaining strong channels with smaller applied voltages. The MOS capacitor is also part of the MOSFET structure.

Early history

Background

The basic principle of the field-effect transistor (FET) was first proposed by Austro-Hungarian physicist Julius Edgar Lilienfeld in 1926, when he filed the first patent for an insulated-gate field-effect transistor.[6] Over the course of next two years he described various FET structures. In his MOS configuration aluminum stood for M, aluminum oxide stood for O, while copper sulfide was used as a semiconductor. However, he was unable to build a practical working FET device.[7] The FET concept was later also theorized by German engineer Oskar Heil in the 1930s and American physicist William Shockley in the 1940s.[8] There was no working practical FET built at the time, and none of these early FET proposals involved thermally oxidized silicon.[7]

Semiconductor companies initially focused on bipolar junction transistors (BJTs) in the early years of the semiconductor industry. However, the junction transistor was a relatively bulky device that was difficult to manufacture on a mass-production basis, which limited it to a number of specialised applications. FETs were theorized as potential alternatives to junction transistors, but researchers were unable to build practical FETs, largely due to the troublesome surface state barrier that prevented the external electric field from penetrating into the material.[9] In the 1950s, researchers had largely given up on the FET concept, and instead focused on BJT technology.[10]

In 1955, Carl Frosch and Lincoln Derrick accidentally covered the surface of silicon wafer with a layer of silicon dioxide. They showed that oxide layer prevented certain dopants into the silicon wafer, while allowing for others, thus discovering the passivating effect of oxidation on the semiconductor surface. Their further work demonstrated how to etch small openings in the oxide layer to diffuse dopants into selected areas of the silicon wafer. In 1957, they published a research paper and patented their technique summarizing their work. The technique they developed is known as oxide diffusion masking, which would later be used in the fabrication of MOSFET devices. At Bell Labs, the importance of Frosch's technique was immediately realized since silicon oxides are much more stable than germanium oxides, have better dielectric properties and at the same time could be used as a diffusion mask. Results of their worked circulated around Bell Labs in the form of BTL memos before being published in 1957. At Shockley Semiconductor, Shockley had circulated the preprint of their article in December 1956 to all his senior stuff, including Jean Hoerni.[9][11][12]

Invention

Mohamed M. Atalla at Bell Labs was dealing with the problem of surface states in the late 1950s. He picked up Frosch's work on oxidation, attempting to passivate the surface of silicon through the formation of oxide layer over it. He thought that growing a very thin high quality thermally grown SiO2 on top of a clean silicon wafer would neutralize surface states enough to make a practical working field-effect transistor. He wrote his findings in his BTL memos in 1957, before presenting his work at an Electrochemical Society meeting in 1958.[13][14][15][16][14][8] This was an important development that enabled MOS technology and silicon integrated circuit (IC) chips.[17] The following year, John L. Moll described the MOS capacitor at Stanford University.[18] Atalla's co-workers J.R. Ligenza and W.G. Spitzer, who studied the mechanism of thermally grown oxides, managed to fabricate a high quality Si/SiO2 stack,[7] with Atalla and Kahng making use of their findings.[19][20]

The MOSFET was invented when Mohamed Atalla and Dawon Kahng[14][13] successfully fabricated the first working MOSFET device in November 1959.[21] The device is covered by two patents, each filed separately by Atalla and Kahng in March 1960.[22][23][24][25] They published their results in June 1960,[26] at the Solid-State Device Conference held at Carnegie Mellon University.[27] The same year, Atalla proposed the use of MOSFETs to build MOS integrated circuit (MOS IC) chips, noting the MOSFET's ease of fabrication.[9]

Commercialization

The advantage of the MOSFET was that it was relatively compact and easy to mass produce compared to the competing planar junction transistor,[28] but the MOSFET represented a radically new technology, the adoption of which would have required spurning the progress that Bell had made with the bipolar junction transistor (BJT). The MOSFET was also initially slower and less reliable than the BJT.[29]

In the early 1960s, MOS technology research programs were established by Fairchild Semiconductor, RCA Laboratories, General Microelectronics (led by former Fairchild engineer Frank Wanlass) and IBM.[30] In 1962, Steve R. Hofstein and Fred P. Heiman at RCA built the first MOS integrated circuit chip. The following year, they collected all previous works on FETs and gave a theory of operation of the MOSFET.[31] CMOS was developed by Chih-Tang Sah and Frank Wanlass at Fairchild in 1963.[32] The first CMOS integrated circuit was later built in 1968 by Albert Medwin.

The first formal public announcement of the MOSFET's existence as a potential technology was made in 1963. It was then first commercialized by General Microelectronics in May 1964, followed Fairchild in October 1964. GMe's first MOS contract was with NASA, which used MOSFETs for spacecraft and satellites in the Interplanetary Monitoring Platform (IMP) program and Explorers Program.[30] The early MOSFETs commercialized by General Microelectronics and Fairchild were p-channel (PMOS) devices for logic and switching applications.[8] By the mid-1960s, RCA were using MOSFETs in their consumer products, including FM radio, television and amplifiers.[33] In 1967, Bell Labs researchers Robert Kerwin, Donald Klein and John Sarace developed the self-aligned gate (silicon-gate) MOS transistor, which Fairchild researchers Federico Faggin and Tom Klein adapted for integrated circuits in 1968.[34]

MOS revolution

The development of the MOSFET led to a revolution in electronics technology, called the MOS revolution[35] or MOSFET revolution,[36] fuelling the technological and economic growth of the early semiconductor industry.

The impact of the MOSFET became commercially significant from the late 1960s onwards.[37] This led to a revolution in the electronics industry, which has since impacted daily life in almost every way.[38] The invention of the MOSFET has been cited as the birth of modern electronics[39] and was central to the microcomputer revolution.[40]

Importance

The MOSFET forms the basis of modern electronics,[41] and is the basic element in most modern electronic equipment.[42] It is the most common transistor in electronics,[13] and the most widely used semiconductor device in the world.[43] It has been described as the "workhorse of the electronics industry"[44] and "the base technology" of the late 20th to early 21st centuries.[10] MOSFET scaling and miniaturization (see List of semiconductor scale examples) have been the primary factors behind the rapid exponential growth of electronic semiconductor technology since the 1960s,[45] as the rapid miniaturization of MOSFETs has been largely responsible for the increasing transistor density, increasing performance and decreasing power consumption of integrated circuit chips and electronic devices since the 1960s.[46]

MOSFETs are capable of high scalability (Moore's law and Dennard scaling),[47] with increasing miniaturization,[48] and can be easily scaled down to smaller dimensions.[49] They consume significantly less power, and allow much higher density, than bipolar transistors.[50] MOSFETs thus have much smaller size than BJTs,[51] about 20 times smaller by the early 1990s.[51] MOSFETs also have faster switching speed,[4] with rapid on–off electronic switching that makes them ideal for generating pulse trains,[52] the basis for digital signals.[53][54] in contrast to BJTs which more slowly generate analog signals resembling sine waves.[52] MOSFETs are also cheaper[55] and have relatively simple processing steps, resulting in high manufacturing yield.[49] MOSFETs thus enable large-scale integration (LSI), and are ideal for digital circuits,[56] as well as linear analog circuits.[52]

The MOSFET has been variously described as the most important transistor,[3] the most important device in the electronics industry,[57] arguably the most important device in the computing industry,[58] one of the most important developments in semiconductor technology,[59] and possibly the most important invention in electronics.[60] The MOSFET has been the fundamental building block of modern digital electronics,[10] during the digital revolution,[61] information revolution,[62] information age,[63] and silicon age.[64][65] MOSFETs have been the driving force behind the computer revolution, and the technologies enabled by it.[66][67][68] The rapid progress of the electronics industry during the late 20th to early 21st centuries was achieved by rapid MOSFET scaling (Dennard scaling and Moore's law), down to the level of nanoelectronics in the early 21st century.[69] The MOSFET revolutionized the world during the information age, with its high density enabling a computer to exist on a few small IC chips rather than filling a room,[70] and later making possible digital communications technology such as smartphones.[66]

The MOSFET is the most widely manufactured device in history.[71][72] The MOSFET generates annual sales of $295 billion as of 2015.[73] Between 1960 and 2018, an estimated total of 13 sextillion MOS transistors have been manufactured, accounting for at least 99.9% of all transistors.[71] Digital integrated circuits such as microprocessors and memory devices contain thousands to billions of integrated MOSFETs on each device, providing the basic switching functions required to implement logic gates and data storage. There are also memory devices which contain at least a trillion MOS transistors, such as a 256 GB microSD memory card, larger than the number of stars in the Milky Way galaxy.[44] As of 2010, the operating principles of modern MOSFETs have remained largely the same as the original MOSFET first demonstrated by Mohamed Atalla and Dawon Kahng in 1960.[74][75]

The US Patent and Trademark Office calls the MOSFET a "groundbreaking invention that transformed life and culture around the world"[66] and the Computer History Museum credits it with "irrevocably changing the human experience."[10] The MOSFET was also the basis for Nobel Prize winning breakthroughs such as the quantum Hall effect[76] and the charge-coupled device (CCD),[77] though there was never any Nobel Prize given for the MOSFET itself.[78] In a 2018 note on Jack Kilby's Nobel Prize for Physics for his part in the invention of the integrated circuit, the Royal Swedish Academy of Sciences specifically mentioned the MOSFET and the microprocessor as other important inventions in the evolution of microelectronics.[79] The MOSFET is also included on the list of IEEE milestones in electronics,[80] and its inventors Mohamed Atalla and Dawon Kahng entered the National Inventors Hall of Fame in 2009.[13][14]

Composition

Usually the semiconductor of choice is silicon. Recently, some chip manufacturers, most notably IBM and Intel, have started using a chemical compound of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good semiconductor-to-insulator interfaces, and thus are not suitable for MOSFETs. Research continues on creating insulators with acceptable electrical characteristics on other semiconductor materials.

To overcome the increase in power consumption due to gate current leakage, a high-κ dielectric is used instead of silicon dioxide for the gate insulator, while polysilicon is replaced by metal gates (e.g. Intel, 2009[81]).

The gate is separated from the channel by a thin insulating layer, traditionally of silicon dioxide and later of silicon oxynitride. Some companies have started to introduce a high-κ dielectric and metal gate combination in the 45 nanometer node.

When a voltage is applied between the gate and body terminals, the electric field generated penetrates through the oxide and creates an inversion layer or channel at the semiconductor-insulator interface. The inversion layer provides a channel through which current can pass between source and drain terminals. Varying the voltage between the gate and body modulates the conductivity of this layer and thereby controls the current flow between drain and source. This is known as enhancement mode.

Operation

Metal–oxide–semiconductor structure

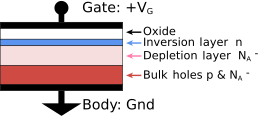

The traditional metal–oxide–semiconductor (MOS) structure is obtained by growing a layer of silicon dioxide (SiO

2) on top of a silicon substrate, commonly by thermal oxidation and depositing a layer of metal or polycrystalline silicon (the latter is commonly used). As the silicon dioxide is a dielectric material, its structure is equivalent to a planar capacitor, with one of the electrodes replaced by a semiconductor.

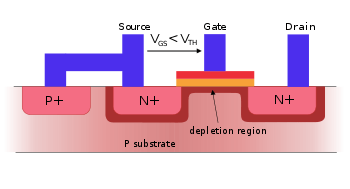

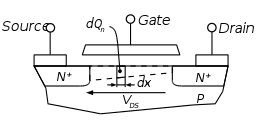

When a voltage is applied across a MOS structure, it modifies the distribution of charges in the semiconductor. If we consider a p-type semiconductor (with the density of acceptors, p the density of holes; p = NA in neutral bulk), a positive voltage, , from gate to body (see figure) creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions (see doping (semiconductor)). If is high enough, a high concentration of negative charge carriers forms in an inversion layer located in a thin layer next to the interface between the semiconductor and the insulator.

Conventionally, the gate voltage at which the volume density of electrons in the inversion layer is the same as the volume density of holes in the body is called the threshold voltage. When the voltage between transistor gate and source (VGS) exceeds the threshold voltage (Vth), the difference is known as overdrive voltage.

This structure with p-type body is the basis of the n-type MOSFET, which requires the addition of n-type source and drain regions.

MOS capacitors and band diagrams

The MOS capacitor structure is the heart of the MOSFET. Consider a MOS capacitor where the silicon base is of p-type. If a positive voltage is applied at the gate, holes which are at the surface of the p-type substrate will be repelled by the electric field generated by the voltage applied. At first, the holes will simply be repelled and what will remain on the surface will be immobile (negative) atoms of the acceptor type, which creates a depletion region on the surface. Remember that a hole is created by an acceptor atom, e.g. Boron, which has one less electron than Silicon. One might ask how can holes be repelled if they are actually non-entities? The answer is that what really happens is not that a hole is repelled, but electrons are attracted by the positive field, and fill these holes, creating a depletion region where no charge carriers exist because the electron is now fixed onto the atom and immobile.

As the voltage at the gate increases, there will be a point at which the surface above the depletion region will be converted from p-type into n-type, as electrons from the bulk area will start to get attracted by the larger electric field. This is known as inversion. The threshold voltage at which this conversion happens is one of the most important parameters in a MOSFET.

In the case of a p-type bulk, inversion happens when the intrinsic energy level at the surface becomes smaller than the Fermi level at the surface. One can see this from a band diagram. Remember that the Fermi level defines the type of semiconductor in discussion. If the Fermi level is equal to the Intrinsic level, the semiconductor is of intrinsic, or pure type. If the Fermi level lies closer to the conduction band (valence band) then the semiconductor type will be of n-type (p-type). Therefore, when the gate voltage is increased in a positive sense (for the given example), this will "bend" the intrinsic energy level band so that it will curve downwards towards the valence band. If the Fermi level lies closer to the valence band (for p-type), there will be a point when the Intrinsic level will start to cross the Fermi level and when the voltage reaches the threshold voltage, the intrinsic level does cross the Fermi level, and that is what is known as inversion. At that point, the surface of the semiconductor is inverted from p-type into n-type. Remember that as said above, if the Fermi level lies above the Intrinsic level, the semiconductor is of n-type, therefore at Inversion, when the Intrinsic level reaches and crosses the Fermi level (which lies closer to the valence band), the semiconductor type changes at the surface as dictated by the relative positions of the Fermi and Intrinsic energy levels.

Structure and channel formation

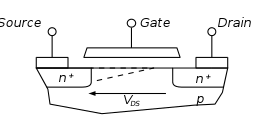

A MOSFET is based on the modulation of charge concentration by a MOS capacitance between a body electrode and a gate electrode located above the body and insulated from all other device regions by a gate dielectric layer. If dielectrics other than an oxide are employed, the device may be referred to as a metal-insulator-semiconductor FET (MISFET). Compared to the MOS capacitor, the MOSFET includes two additional terminals (source and drain), each connected to individual highly doped regions that are separated by the body region. These regions can be either p or n type, but they must both be of the same type, and of opposite type to the body region. The source and drain (unlike the body) are highly doped as signified by a "+" sign after the type of doping.

If the MOSFET is an n-channel or nMOS FET, then the source and drain are n+ regions and the body is a p region. If the MOSFET is a p-channel or pMOS FET, then the source and drain are p+ regions and the body is a n region. The source is so named because it is the source of the charge carriers (electrons for n-channel, holes for p-channel) that flow through the channel; similarly, the drain is where the charge carriers leave the channel.

The occupancy of the energy bands in a semiconductor is set by the position of the Fermi level relative to the semiconductor energy-band edges.

With sufficient gate voltage, the valence band edge is driven far from the Fermi level, and holes from the body are driven away from the gate.

At larger gate bias still, near the semiconductor surface the conduction band edge is brought close to the Fermi level, populating the surface with electrons in an inversion layer or n-channel at the interface between the p region and the oxide. This conducting channel extends between the source and the drain, and current is conducted through it when a voltage is applied between the two electrodes. Increasing the voltage on the gate leads to a higher electron density in the inversion layer and therefore increases the current flow between the source and drain. For gate voltages below the threshold value, the channel is lightly populated, and only a very small subthreshold leakage current can flow between the source and the drain.

When a negative gate–source voltage is applied, it creates a p-channel at the surface of the n region, analogous to the n-channel case, but with opposite polarities of charges and voltages. When a voltage less negative than the threshold value (a negative voltage for the p-channel) is applied between gate and source, the channel disappears and only a very small subthreshold current can flow between the source and the drain. The device may comprise a silicon on insulator device in which a buried oxide is formed below a thin semiconductor layer. If the channel region between the gate dielectric and the buried oxide region is very thin, the channel is referred to as an ultrathin channel region with the source and drain regions formed on either side in or above the thin semiconductor layer. Other semiconductor materials may be employed. When the source and drain regions are formed above the channel in whole or in part, they are referred to as raised source/drain regions.

| Parameter | nMOSFET | pMOSFET | |

|---|---|---|---|

| Source/drain type | n-type | p-type | |

| Channel type (MOS capacitor) |

n-type | p-type | |

| Gate type |

Polysilicon | n+ | p+ |

| Metal | φm ~ Si conduction band | φm ~ Si valence band | |

| Well type | p-type | n-type | |

| Threshold voltage, Vth |

|

| |

| Band-bending | Downwards | Upwards | |

| Inversion layer carriers | Electrons | Holes | |

| Substrate type | p-type | n-type | |

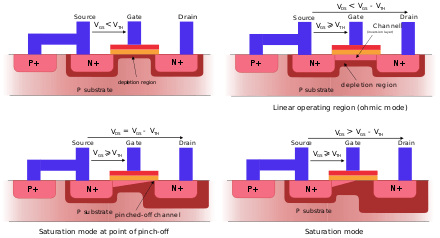

Modes of operation

top left: Subthreshold, top right: Ohmic mode, bottom left: Active mode at onset of pinch-off, bottom right: Active mode well into pinch-off – channel length modulation evident

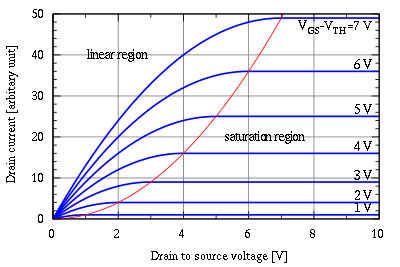

The operation of a MOSFET can be separated into three different modes, depending on the voltages at the terminals. In the following discussion, a simplified algebraic model is used.[84] Modern MOSFET characteristics are more complex than the algebraic model presented here.[85]

For an enhancement-mode, n-channel MOSFET, the three operational modes are:

- Cutoff, subthreshold, and weak-inversion mode

When VGS < Vth:

where is gate-to-source bias and is the threshold voltage of the device.

According to the basic threshold model, the transistor is turned off, and there is no conduction between drain and source. A more accurate model considers the effect of thermal energy on the Fermi–Dirac distribution of electron energies which allow some of the more energetic electrons at the source to enter the channel and flow to the drain. This results in a subthreshold current that is an exponential function of gate–source voltage. While the current between drain and source should ideally be zero when the transistor is being used as a turned-off switch, there is a weak-inversion current, sometimes called subthreshold leakage.

In weak inversion where the source is tied to bulk, the current varies exponentially with as given approximately by:[86][87]

where = current at , the thermal voltage and the slope factor n is given by:

with = capacitance of the depletion layer and = capacitance of the oxide layer. This equation is generally used, but is only an adequate approximation for the source tied to the bulk. For the source not tied to the bulk, the subthreshold equation for drain current in saturation is[88][89]

where the is the channel divider that is given by:

with = capacitance of the depletion layer and = capacitance of the oxide layer. In a long-channel device, there is no drain voltage dependence of the current once , but as channel length is reduced drain-induced barrier lowering introduces drain voltage dependence that depends in a complex way upon the device geometry (for example, the channel doping, the junction doping and so on). Frequently, threshold voltage Vth for this mode is defined as the gate voltage at which a selected value of current ID0 occurs, for example, ID0 = 1 μA, which may not be the same Vth-value used in the equations for the following modes.

Some micropower analog circuits are designed to take advantage of subthreshold conduction.[90][91][92] By working in the weak-inversion region, the MOSFETs in these circuits deliver the highest possible transconductance-to-current ratio, namely: , almost that of a bipolar transistor.[93]

The subthreshold I–V curve depends exponentially upon threshold voltage, introducing a strong dependence on any manufacturing variation that affects threshold voltage; for example: variations in oxide thickness, junction depth, or body doping that change the degree of drain-induced barrier lowering. The resulting sensitivity to fabricational variations complicates optimization for leakage and performance.[94][95]

When VGS > Vth and VDS < VGS − Vth:

The transistor is turned on, and a channel has been created which allows current between the drain and the source. The MOSFET operates like a resistor, controlled by the gate voltage relative to both the source and drain voltages. The current from drain to source is modeled as:

where is the charge-carrier effective mobility, is the gate width, is the gate length and is the gate oxide capacitance per unit area. The transition from the exponential subthreshold region to the triode region is not as sharp as the equations suggest.

When VGS > Vth and VDS ≥ (VGS – Vth):

The switch is turned on, and a channel has been created, which allows current between the drain and source. Since the drain voltage is higher than the source voltage, the electrons spread out, and conduction is not through a narrow channel but through a broader, two- or three-dimensional current distribution extending away from the interface and deeper in the substrate. The onset of this region is also known as pinch-off to indicate the lack of channel region near the drain. Although the channel does not extend the full length of the device, the electric field between the drain and the channel is very high, and conduction continues. The drain current is now weakly dependent upon drain voltage and controlled primarily by the gate–source voltage, and modeled approximately as:

The additional factor involving λ, the channel-length modulation parameter, models current dependence on drain voltage due to the channel length modulation, effectively similar to the Early effect seen in bipolar devices. According to this equation, a key design parameter, the MOSFET transconductance is:

where the combination Vov = VGS − Vth is called the overdrive voltage,[100] and where VDSsat = VGS − Vth accounts for a small discontinuity in which would otherwise appear at the transition between the triode and saturation regions.

Another key design parameter is the MOSFET output resistance given by:

- .

rout is the inverse of gDS where . ID is the expression in saturation region.

If λ is taken as zero, the resulting infinite output resistance can simplify circuit analysis, however this may lead to unrealistic circuit predictions, particularly in analog circuits.

As the channel length becomes very short, these equations become quite inaccurate. New physical effects arise. For example, carrier transport in the active mode may become limited by velocity saturation. When velocity saturation dominates, the saturation drain current is more nearly linear than quadratic in VGS. At even shorter lengths, carriers transport with near zero scattering, known as quasi-ballistic transport. In the ballistic regime, the carriers travel at an injection velocity that may exceed the saturation velocity and approaches the Fermi velocity at high inversion charge density. In addition, drain-induced barrier lowering increases off-state (cutoff) current and requires an increase in threshold voltage to compensate, which in turn reduces the saturation current.

Body effect

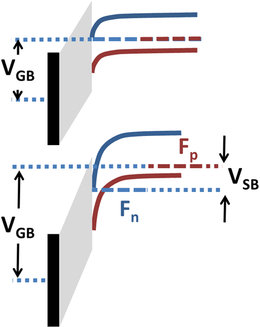

The occupancy of the energy bands in a semiconductor is set by the position of the Fermi level relative to the semiconductor energy-band edges. Application of a source-to-substrate reverse bias of the source-body pn-junction introduces a split between the Fermi levels for electrons and holes, moving the Fermi level for the channel further from the band edge, lowering the occupancy of the channel. The effect is to increase the gate voltage necessary to establish the channel, as seen in the figure. This change in channel strength by application of reverse bias is called the 'body effect'.

Simply put, using an nMOS example, the gate-to-body bias VGB positions the conduction-band energy levels, while the source-to-body bias VSB positions the electron Fermi level near the interface, deciding occupancy of these levels near the interface, and hence the strength of the inversion layer or channel.

The body effect upon the channel can be described using a modification of the threshold voltage, approximated by the following equation:

where VTB is the threshold voltage with substrate bias present, and VT0 is the zero-VSB value of threshold voltage, is the body effect parameter, and 2φB is the approximate potential drop between surface and bulk across the depletion layer when VSB = 0 and gate bias is sufficient to ensure that a channel is present.[101] As this equation shows, a reverse bias VSB > 0 causes an increase in threshold voltage VTB and therefore demands a larger gate voltage before the channel populates.

The body can be operated as a second gate, and is sometimes referred to as the "back gate"; the body effect is sometimes called the "back-gate effect".[102]

Circuit symbols

A variety of symbols are used for the MOSFET. The basic design is generally a line for the channel with the source and drain leaving it at right angles and then bending back at right angles into the same direction as the channel. Sometimes three line segments are used for enhancement mode and a solid line for depletion mode (see depletion and enhancement modes). Another line is drawn parallel to the channel for the gate.

The bulk or body connection, if shown, is shown connected to the back of the channel with an arrow indicating pMOS or nMOS. Arrows always point from P to N, so an NMOS (N-channel in P-well or P-substrate) has the arrow pointing in (from the bulk to the channel). If the bulk is connected to the source (as is generally the case with discrete devices) it is sometimes angled to meet up with the source leaving the transistor. If the bulk is not shown (as is often the case in IC design as they are generally common bulk) an inversion symbol is sometimes used to indicate PMOS, alternatively an arrow on the source may be used in the same way as for bipolar transistors (out for nMOS, in for pMOS).

Comparison of enhancement-mode and depletion-mode MOSFET symbols, along with JFET symbols. The orientation of the symbols, (most significantly the position of source relative to drain) is such that more positive voltages appear higher on the page than less positive voltages, implying current flowing "down" the page:[103][104][105]

| P-channel |  |

|

|

|

|

|---|---|---|---|---|---|

| N-channel |  |

|

|

|

|

| JFET | MOSFET enh. | MOSFET enh. (no bulk) | MOSFET dep. | ||

In schematics where G, S, D are not labeled, the detailed features of the symbol indicate which terminal is source and which is drain. For enhancement-mode and depletion-mode MOSFET symbols (in columns two and five), the source terminal is the one connected to the arrowhead. Additionally, in this diagram, the gate is shown as an "L" shape, whose input leg is closer to S than D, also indicating which is which. However, these symbols are often drawn with a "T" shaped gate (as elsewhere on this page), so it is the arrowhead which must be relied upon to indicate the source terminal.

For the symbols in which the bulk, or body, terminal is shown, it is here shown internally connected to the source (i.e., the black arrowhead in the diagrams in columns 2 and 5). This is a typical configuration, but by no means the only important configuration. In general, the MOSFET is a four-terminal device, and in integrated circuits many of the MOSFETs share a body connection, not necessarily connected to the source terminals of all the transistors.

Types of MOSFET

PMOS and NMOS logic

P-channel MOS (PMOS) logic uses p-channel MOSFETs to implement logic gates and other digital circuits. N-channel MOS (NMOS) logic uses n-channel MOSFETs to implement logic gates and other digital circuits.

For devices of equal current driving capability, n-channel MOSFETs can be made smaller than p-channel MOSFETs, due to p-channel charge carriers (holes) having lower mobility than do n-channel charge carriers (electrons), and producing only one type of MOSFET on a silicon substrate is cheaper and technically simpler. These were the driving principles in the design of NMOS logic which uses n-channel MOSFETs exclusively. However, unlike CMOS logic (neglecting leakage current), NMOS logic consumes power even when no switching is taking place.

Mohamed Atalla and Dawon Kahng originally demonstrated both pMOS and nMOS devices with 20 µm and then 10 µm gate lengths in 1960.[15][106] Their original MOSFET devices also had a gate oxide thickness of 100 nm.[107] However, the nMOS devices were impractical, and only the pMOS type were practical working devices.[15] A more practical NMOS process was developed several years later. NMOS was initially faster than CMOS, thus NMOS was more widely used for computers in the 1970s.[108] With advances in technology, CMOS logic displaced NMOS logic in the mid-1980s to become the preferred process for digital chips.

Complementary MOS (CMOS)

The MOSFET is used in digital complementary metal–oxide–semiconductor (CMOS) logic,[109] which uses p- and n-channel MOSFETs as building blocks. Overheating is a major concern in integrated circuits since ever more transistors are packed into ever smaller chips. CMOS logic reduces power consumption because no current flows (ideally), and thus no power is consumed, except when the inputs to logic gates are being switched. CMOS accomplishes this current reduction by complementing every nMOSFET with a pMOSFET and connecting both gates and both drains together. A high voltage on the gates will cause the nMOSFET to conduct and the pMOSFET not to conduct and a low voltage on the gates causes the reverse. During the switching time as the voltage goes from one state to another, both MOSFETs will conduct briefly. This arrangement greatly reduces power consumption and heat generation.

CMOS was developed by Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor in 1963.[32] CMOS had lower power consumption, but was initially slower than NMOS, which was more widely used for computers in the 1970s. In 1978, Hitachi introduced the twin-well CMOS process, which allowed CMOS to match the performance of NMOS with less power consumption. The twin-well CMOS process eventually overtook NMOS as the most common semiconductor manufacturing process for computers in the 1980s.[108] By the 1970s–1980s, CMOS logic consumed over 7 times less power than NMOS logic,[108] and about 100,000 times less power than bipolar transistor-transistor logic (TTL).[110]

Depletion-mode

There are depletion-mode MOSFET devices, which are less commonly used than the standard enhancement-mode devices already described. These are MOSFET devices that are doped so that a channel exists even with zero voltage from gate to source. To control the channel, a negative voltage is applied to the gate (for an n-channel device), depleting the channel, which reduces the current flow through the device. In essence, the depletion-mode device is equivalent to a normally closed (on) switch, while the enhancement-mode device is equivalent to a normally open (off) switch.[111]

Due to their low noise figure in the RF region, and better gain, these devices are often preferred to bipolars in RF front-ends such as in TV sets.

Depletion-mode MOSFET families include BF960 by Siemens and Telefunken, and the BF980 in the 1980s by Philips (later to become NXP Semiconductors), whose derivatives are still used in AGC and RF mixer front-ends.

Metal–insulator–semiconductor field-effect transistor (MISFET)

Metal–insulator–semiconductor field-effect-transistor,[112][113][114] or MISFET, is a more general term than MOSFET and a synonym to insulated-gate field-effect transistor (IGFET). All MOSFETs are MISFETs, but not all MISFETs are MOSFETs.

The gate dielectric insulator in a MISFET is silicon dioxide in a MOSFET, but other materials can also be employed. The gate dielectric lies directly below the gate electrode and above the channel of the MISFET. The term metal is historically used for the gate material, even though now it is usually highly doped polysilicon or some other non-metal.

Insulator types may be:

- Silicon dioxide, in MOSFETs

- Organic insulators (e.g., undoped trans-polyacetylene; cyanoethyl pullulan, CEP[115]), for organic-based FETs.[114]

Floating-gate MOSFET (FGMOS)

The floating-gate MOSFET (FGMOS) is a type of MOSFET where the gate is electrically isolated, creating a floating node in DC and a number of secondary gates or inputs are deposited above the floating gate (FG) and are electrically isolated from it. The first report of a floating-gate MOSFET (FGMOS) was made by Dawon Kahng (co-inventor of the original MOSFET) and Simon Sze in 1967.[116]

The FGMOS is commonly used as a floating-gate memory cell, the digital storage element in EPROM, EEPROM and flash memories. Other uses of the FGMOS include a neuronal computational element in neural networks, analog storage element, digital potentiometers and single-transistor DACs.

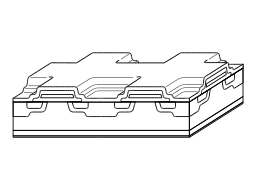

Power MOSFET

Power MOSFETs have a different structure.[117] As with most power devices, the structure is vertical and not planar. Using a vertical structure, it is possible for the transistor to sustain both high blocking voltage and high current. The voltage rating of the transistor is a function of the doping and thickness of the N-epitaxial layer (see cross section), while the current rating is a function of the channel width (the wider the channel, the higher the current). In a planar structure, the current and breakdown voltage ratings are both a function of the channel dimensions (respectively width and length of the channel), resulting in inefficient use of the "silicon estate". With the vertical structure, the component area is roughly proportional to the current it can sustain, and the component thickness (actually the N-epitaxial layer thickness) is proportional to the breakdown voltage.[118]

Power MOSFETs with lateral structure are mainly used in high-end audio amplifiers and high-power PA systems. Their advantage is a better behaviour in the saturated region (corresponding to the linear region of a bipolar transistor) than the vertical MOSFETs. Vertical MOSFETs are designed for switching applications.[119]

The power MOSFET, which is commonly used in power electronics, was developed in the early 1970s.[120] The power MOSFET enables low gate drive power, fast switching speed, and advanced paralleling capability.[4]

Double-diffused metal–oxide–semiconductor (DMOS)

There are VDMOS (vertical double-diffused metal oxide semiconductor) and LDMOS (lateral double-diffused metal oxide semiconductor). Most power MOSFETs are made using this technology.

MOS capacitor

The MOS capacitor is part of the MOSFET structure, where the MOS capacitor is flanked by two p-n junctions.[121] The MOS capacitor is widely used as a storage capacitor in memory chips, and as the basic building block of the charge-coupled device (CCD) in image sensor technology.[122] In DRAM (dynamic random-access memory), each memory cell typically consists of a MOSFET and MOS capacitor.[123]

Thin-film transistor (TFT)

The thin-film transistor (TFT) is a type of MOSFET distinct from the standard bulk MOSFET.[124] The first TFT was invented by Paul K. Weimer at RCA in 1962, building on the earlier work of Atalla and Kahng on MOSFETs.[125]

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968.[126] Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated the concept in 1968 with an 18x2 matrix dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.[127]

Bipolar–MOS transistors

BiCMOS is an integrated circuit that combines BJT and CMOS transistors on a single chip.[128]

The insulated-gate bipolar transistor (IGBT) is a power transistor with characteristics of both a MOSFET and bipolar junction transistor (BJT).[129]

MOS sensors

A number of MOSFET sensors have been developed, for measuring physical, chemical, biological and environmental parameters.[130] The earliest MOSFET sensors include the open-gate FET (OGFET) introduced by Johannessen in 1970,[130] the ion-sensitive field-effect transistor (ISFET) invented by Piet Bergveld in 1970,[131] the adsorption FET (ADFET) patented by P.F. Cox in 1974, and a hydrogen-sensitive MOSFET demonstrated by I. Lundstrom, M.S. Shivaraman, C.S. Svenson and L. Lundkvist in 1975.[130] The ISFET is a special type of MOSFET with a gate at a certain distance,[130] and where the metal gate is replaced by an ion-sensitive membrane, electrolyte solution and reference electrode.[132]

By the mid-1980s, numerous other MOSFET sensors had been developed, including the gas sensor FET (GASFET), surface accessible FET (SAFET), charge flow transistor (CFT), pressure sensor FET (PRESSFET), chemical field-effect transistor (ChemFET), reference ISFET (REFET), biosensor FET (BioFET), enzyme-modified FET (ENFET) and immunologically modified FET (IMFET).[130] By the early 2000s, BioFET types such as the DNA field-effect transistor (DNAFET), gene-modified FET (GenFET) and cell-potential BioFET (CPFET) had been developed.[132]

The two main types of image sensors used in digital imaging technology are the charge-coupled device (CCD) and the active-pixel sensor (CMOS sensor). Both CCD and CMOS sensors are based on MOS technology, with the CCD based on MOS capacitors and the CMOS sensor based on MOS transistors.[77]

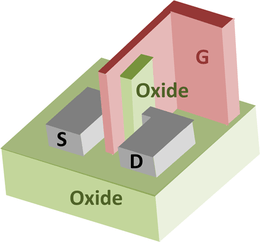

Multi-gate field-effect transistor (MuGFET)

The dual-gate MOSFET (DGMOS) has a tetrode configuration, where both gates control the current in the device. It is commonly used for small-signal devices in radio frequency applications where biasing the drain-side gate at constant potential reduces the gain loss caused by Miller effect, replacing two separate transistors in cascode configuration. Other common uses in RF circuits include gain control and mixing (frequency conversion). The tetrode description, though accurate, does not replicate the vacuum-tube tetrode. Vacuum-tube tetrodes, using a screen grid, exhibit much lower grid-plate capacitance and much higher output impedance and voltage gains than triode vacuum tubes. These improvements are commonly an order of magnitude (10 times) or considerably more. Tetrode transistors (whether bipolar junction or field-effect) do not exhibit improvements of such a great degree.

The FinFET is a double-gate silicon-on-insulator device, one of a number of geometries being introduced to mitigate the effects of short channels and reduce drain-induced barrier lowering. The fin refers to the narrow channel between source and drain. A thin insulating oxide layer on either side of the fin separates it from the gate. SOI FinFETs with a thick oxide on top of the fin are called double-gate and those with a thin oxide on top as well as on the sides are called triple-gate FinFETs.[133][134]

A double-gate MOSFET transistor was first demonstrated in 1984 by Electrotechnical Laboratory researchers Toshihiro Sekigawa and Yutaka Hayashi.[135][136] A GAAFET (gate-all-around MOSFET), a type of multi-gate non-planar 3D transistor, was first demonstrated in 1988 by a Toshiba research team including Fujio Masuoka, H. Takato and K. Sunouchi.[137][138] The FinFET (fin field-effect transistor), a type of 3D non-planar double-gate MOSFET, originated from the research of Digh Hisamoto and his team at Hitachi Central Research Laboratory in 1989.[139][140] The development of nanowire multi-gate MOSFETs have since become fundamental to nanoelectronics.[141]

Quantum field-effect transistor (QFET)

A quantum field-effect transistor (QFET) or quantum well field-effect transistor (QWFET) is a type of MOSFET[142][143][144] that takes advantage of quantum tunneling to greatly increase the speed of transistor operation.[145]

Radiation-hardened-by-design (RHBD)

Semiconductor sub-micrometer and nanometer electronic circuits are the primary concern for operating within the normal tolerance in harsh radiation environments like outer space. One of the design approaches for making a radiation-hardened-by-design (RHBD) device is enclosed-layout-transistor (ELT). Normally, the gate of the MOSFET surrounds the drain, which is placed in the center of the ELT. The source of the MOSFET surrounds the gate. Another RHBD MOSFET is called H-Gate. Both of these transistors have very low leakage current with respect to radiation. However, they are large in size and take more space on silicon than a standard MOSFET. In older STI (shallow trench isolation) designs, radiation strikes near the silicon oxide region cause the channel inversion at the corners of the standard MOSFET due to accumulation of radiation induced trapped charges. If the charges are large enough, the accumulated charges affect STI surface edges along the channel near the channel interface (gate) of the standard MOSFET. Thus the device channel inversion occurs along the channel edges and the device creates an off-state leakage path, causing the device to turn on. So the reliability of circuits degrades severely. The ELT offers many advantages. These advantages include improvement of reliability by reducing unwanted surface inversion at the gate edges that occurs in the standard MOSFET. Since the gate edges are enclosed in ELT, there is no gate oxide edge (STI at gate interface), and thus the transistor off-state leakage is reduced considerably. Low-power microelectronic circuits including computers, communication devices and monitoring systems in the space shuttle and satellites are very different to what is used on earth. They require radiation (high-speed atomic particles like proton and neutron, solar flare magnetic energy dissipation in Earth's space, energetic cosmic rays like X-ray, gamma ray etc.) tolerant circuits. These special electronics are designed by applying different techniques using RHBD MOSFETs to ensure safer journeys and space-walks for astronauts.

Applications

The MOSFET generally forms the basis of modern electronics,[41] as the dominant transistor in digital circuits as well as analog integrated circuits.[3] It is the basis for numerous modern technologies,[146] and is commonly used for a wide range of applications.[46] According to Jean-Pierre Colinge, numerous modern technologies would not exist without the MOSFET, such as the modern computer industry, digital telecommunication systems, video games, pocket calculators, and digital wristwatches, for example.[146]

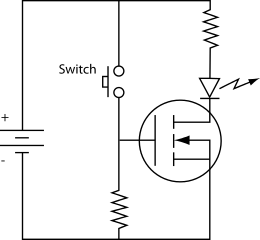

Discrete MOSFET devices are widely used in applications such as switch mode power supplies, variable-frequency drives and other power electronics applications where each device may be switching thousands of watts. Radio-frequency amplifiers up to the UHF spectrum use MOSFET transistors as analog signal and power amplifiers. Radio systems also use MOSFETs as oscillators, or mixers to convert frequencies. MOSFET devices are also applied in audio-frequency power amplifiers for public address systems, sound reinforcement and home and automobile sound systems.

MOSFETs in integrated circuits are the primary elements of computer processors, semiconductor memory, image sensors, and most other types of integrated circuits.

MOS integrated circuit (MOS IC)

The MOSFET is the most widely used type of transistor and the most critical device component in integrated circuit (IC) chips.[147] The monolithic integrated circuit chip was enabled by the surface passivation process, which electrically stabilized silicon surfaces via thermal oxidation, making it possible to fabricate monolithic integrated circuit chips using silicon. The surface passivation process was developed by Mohamed M. Atalla at Bell Labs in 1957. This was the basis for the planar process, developed by Jean Hoerni at Fairchild Semiconductor in early 1959, which was critical to the invention of the monolithic integrated circuit chip by Robert Noyce later in 1959.[148][149][17] The same year,[8] Atalla used his surface passivation process to invent the MOSFET with Dawon Kahng at Bell Labs.[14][13] This was followed by the development of clean rooms to reduce contamination to levels never before thought necessary, and coincided with the development of photolithography[150] which, along with surface passivation and the planar process, allowed circuits to be made in few steps.

Mohamed Atalla first proposed the concept of the MOS integrated circuit (MOS IC) chip in 1960, noting that the MOSFET's ease of fabrication made it useful for integrated circuits.[9] In contrast to bipolar transistors which required a number of steps for the p–n junction isolation of transistors on a chip, MOSFETs required no such steps but could be easily isolated from each other.[29] Its advantage for integrated circuits was re-iterated by Dawon Kahng in 1961.[21] The Si–SiO2 system possessed the technical attractions of low cost of production (on a per circuit basis) and ease of integration. These two factors, along with its rapidly scaling miniaturization and low energy consumption, led to the MOSFET becoming the most widely used type of transistor in IC chips.

The earliest experimental MOS IC to be demonstrated was a 16-transistor chip built by Fred Heiman and Steven Hofstein at RCA in 1962.[55] General Microelectronics later introduced the first commercial MOS integrated circuits in 1964, consisting of 120 p-channel transistors.[151] It was a 20-bit shift register, developed by Robert Norman[55] and Frank Wanlass.[152] In 1968, Fairchild Semiconductor researchers Federico Faggin and Tom Klein developed the first silicon-gate MOS IC.[34]

MOS large-scale integration (MOS LSI)

With its high scalability,[47] and much lower power consumption and higher density than bipolar junction transistors,[50] the MOSFET made it possible to build high-density IC chips.[1] By 1964, MOS chips had reached higher transistor density and lower manufacturing costs than bipolar chips. MOS chips further increased in complexity at a rate predicted by Moore's law, leading to large-scale integration (LSI) with hundreds of MOSFETs on a chip by the late 1960s.[153] MOS technology enabled the integration of more than 10,000 transistors on a single LSI chip by the early 1970s,[154] before later enabling very large-scale integration (VLSI).[49][155]

Microprocessors

The MOSFET is the basis of every microprocessor,[44] and was responsible for the invention of the microprocessor.[156] The origins of both the microprocessor and the microcontroller can be traced back to the invention and development of MOS technology. The application of MOS LSI chips to computing was the basis for the first microprocessors, as engineers began recognizing that a complete computer processor could be contained on a single MOS LSI chip.[153]

The earliest microprocessors were all MOS chips, built with MOS LSI circuits. The first multi-chip microprocessors, the Four-Phase Systems AL1 in 1969 and the Garrett AiResearch MP944 in 1970, were developed with multiple MOS LSI chips. The first commercial single-chip microprocessor, the Intel 4004, was developed by Federico Faggin, using his silicon-gate MOS IC technology, with Intel engineers Marcian Hoff and Stan Mazor, and Busicom engineer Masatoshi Shima.[157] With the arrival of CMOS microprocessors in 1975, the term "MOS microprocessors" began to refer to chips fabricated entirely from PMOS logic or fabricated entirely from NMOS logic, contrasted with "CMOS microprocessors" and "bipolar bit-slice processors".[158]

CMOS circuits

Digital

The growth of digital technologies like the microprocessor has provided the motivation to advance MOSFET technology faster than any other type of silicon-based transistor.[159] A big advantage of MOSFETs for digital switching is that the oxide layer between the gate and the channel prevents DC current from flowing through the gate, further reducing power consumption and giving a very large input impedance. The insulating oxide between the gate and channel effectively isolates a MOSFET in one logic stage from earlier and later stages, which allows a single MOSFET output to drive a considerable number of MOSFET inputs. Bipolar transistor-based logic (such as TTL) does not have such a high fanout capacity. This isolation also makes it easier for the designers to ignore to some extent loading effects between logic stages independently. That extent is defined by the operating frequency: as frequencies increase, the input impedance of the MOSFETs decreases.

Analog

The MOSFET's advantages in digital circuits do not translate into supremacy in all analog circuits. The two types of circuit draw upon different features of transistor behavior. Digital circuits switch, spending most of their time either fully on or fully off. The transition from one to the other is only of concern with regards to speed and charge required. Analog circuits depend on operation in the transition region where small changes to Vgs can modulate the output (drain) current. The JFET and bipolar junction transistor (BJT) are preferred for accurate matching (of adjacent devices in integrated circuits), higher transconductance and certain temperature characteristics which simplify keeping performance predictable as circuit temperature varies.

Nevertheless, MOSFETs are widely used in many types of analog circuits because of their own advantages (zero gate current, high and adjustable output impedance and improved robustness vs. BJTs which can be permanently degraded by even lightly breaking down the emitter-base). The characteristics and performance of many analog circuits can be scaled up or down by changing the sizes (length and width) of the MOSFETs used. By comparison, in bipolar transistors the size of the device does not significantly affect its performance. MOSFETs' ideal characteristics regarding gate current (zero) and drain-source offset voltage (zero) also make them nearly ideal switch elements, and also make switched capacitor analog circuits practical. In their linear region, MOSFETs can be used as precision resistors, which can have a much higher controlled resistance than BJTs. In high power circuits, MOSFETs sometimes have the advantage of not suffering from thermal runaway as BJTs do. Also, MOSFETs can be configured to perform as capacitors and gyrator circuits which allow op-amps made from them to appear as inductors, thereby allowing all of the normal analog devices on a chip (except for diodes, which can be made smaller than a MOSFET anyway) to be built entirely out of MOSFETs. This means that complete analog circuits can be made on a silicon chip in a much smaller space and with simpler fabrication techniques. MOSFETS are ideally suited to switch inductive loads because of tolerance to inductive kickback.

Some ICs combine analog and digital MOSFET circuitry on a single mixed-signal integrated circuit, making the needed board space even smaller. This creates a need to isolate the analog circuits from the digital circuits on a chip level, leading to the use of isolation rings and silicon on insulator (SOI). Since MOSFETs require more space to handle a given amount of power than a BJT, fabrication processes can incorporate BJTs and MOSFETs into a single device. Mixed-transistor devices are called bi-FETs (bipolar FETs) if they contain just one BJT-FET and BiCMOS (bipolar-CMOS) if they contain complementary BJT-FETs. Such devices have the advantages of both insulated gates and higher current density.

In the late 1980s, Asad Abidi pioneered RF CMOS technology, which uses MOS VLSI circuits, while working at UCLA. This changed the way in which RF circuits were designed, away from discrete bipolar transistors and towards CMOS integrated circuits. As of 2008, the radio transceivers in all wireless networking devices and modern mobile phones are mass-produced as RF CMOS devices. RF CMOS is also used in nearly all modern Bluetooth and wireless LAN (WLAN) devices.[160]

MOS memory

The advent of the MOSFET enabled the practical use of MOS transistors as memory cell storage elements, a function previously served by magnetic cores in computer memory.[62] The first modern computer memory was introduced in 1965, when John Schmidt at Fairchild Semiconductor designed the first MOS semiconductor memory, a 64-bit MOS SRAM (static random-access memory).[161] SRAM became an alternative to magnetic-core memory, but required six MOS transistors for each bit of data.[162]

MOS technology is the basis for DRAM (dynamic random-access memory). In 1966, Dr. Robert H. Dennard at the IBM Thomas J. Watson Research Center was working on MOS memory. While examining the characteristics of MOS technology, he found it was capable of building capacitors, and that storing a charge or no charge on the MOS capacitor could represent the 1 and 0 of a bit, while the MOS transistor could control writing the charge to the capacitor. This led to his development of a single-transistor DRAM memory cell.[162] In 1967, Dennard filed a patent under IBM for a single-transistor DRAM (dynamic random-access memory) memory cell, based on MOS technology.[163] MOS memory enabled higher performance, was cheaper, and consumed less power, than magnetic-core memory, leading to MOS memory overtaking magnetic core memory as the dominant computer memory technology by the early 1970s.[164]

Frank Wanlass, while studying MOSFET structures in 1963, noted the movement of charge through oxide onto a gate. While he did not pursue it, this idea would later become the basis for EPROM (erasable programmable read-only memory) technology.[165] In 1967, Dawon Kahng and Simon Sze proposed that floating-gate memory cells, consisting of floating-gate MOSFETs (FGMOS), could be used to produce reprogrammable ROM (read-only memory).[166] Floating-gate memory cells later became the basis for non-volatile memory (NVM) technologies including EPROM, EEPROM (electrically erasable programmable ROM) and flash memory.[167]

Consumer electronics

MOSFETs are widely used in consumer electronics. One of the earliest influential consumer electronic products enabled by MOS LSI circuits was the electronic pocket calculator,[154] as MOS LSI technology enabled large amounts of computational capability in small packages.[168] In 1965, the Victor 3900 desktop calculator was the first MOS calculator, with 29 MOS chips.[169] In 1967, the Texas Instruments Cal-Tech was the first prototype electronic handheld calculator, with three MOS LSI chips, and it was later released as the Canon Pocketronic in 1970.[170] The Sharp QT-8D desktop calculator was the first mass-produced LSI MOS calculator in 1969,[171] and the Sharp EL-8 which used four MOS LSI chips was the first commercial electronic handheld calculator in 1970.[170] The first true electronic pocket calculator was the Busicom LE-120A HANDY LE, which used a single MOS LSI calculator-on-a-chip from Mostek, and was released in 1971.[170] By 1972, MOS LSI circuits were commercialized for numerous other applications.[172]

MOSFETs are fundamental to information and communications technology (ICT),[66][79] including modern computers,[173][146][155] modern computing,[174] telecommunications, the communications infrastructure,[173][175] the Internet,[173][72][176] digital telephony,[177] wireless telecommunications,[178][179] and mobile networks.[179] According to Colinge, the modern computer industry and digital telecommunication systems would not exist without the MOSFET.[146] Advances in MOS technology has been the most important contributing factor in the rapid rise of network bandwidth in telecommunication networks, with bandwidth doubling every 18 months, from bits per second to terabits per second (Edholm's law).[180]

MOS sensors

MOS sensors, also known as MOSFET sensors, are widely used to measure physical, chemical, biological and environmental parameters.[130] The ion-sensitive field-effect transistor (ISFET), for example, is widely used in biomedical applications.[132]

MOSFETs are also widely used in microelectromechanical systems (MEMS), as silicon MOSFETs could interact and communicate with the surroundings and process things such as chemicals, motions and light.[181] An early example of a MEMS device is the resonant-gate transistor, an adaptation of the MOSFET, developed by Harvey C. Nathanson in 1965.[182]

MOS technology is the basis for modern image sensors, including the charge-coupled device (CCD) and the CMOS active-pixel sensor (CMOS sensor), used in digital imaging and digital cameras.[77] Willard Boyle and George E. Smith developed the CCD in 1969. While researching the MOS process, they realized that an electric charge was the analogy of the magnetic bubble and that it could be stored on a tiny MOS capacitor. As it was fairly straighforward to fabricate a series of MOS capacitors in a row, they connected a suitable voltage to them so that the charge could be stepped along from one to the next.[77] The CCD is a semiconductor circuit that was later used in the first digital video cameras for television broadcasting.[183]

The MOS active-pixel sensor (APS) was developed by Tsutomu Nakamura at Olympus in 1985.[184] The CMOS active-pixel sensor was later developed by Eric Fossum and his team at NASA's Jet Propulsion Laboratory in the early 1990s.[185]

MOS image sensors are widely used in optical mouse technology. The first optical mouse, invented by Richard F. Lyon at Xerox in 1980, used a 5 µm NMOS sensor chip.[186][187] Since the first commercial optical mouse, the IntelliMouse introduced in 1999, most optical mouse devices use CMOS sensors.[188]

Power MOSFETs

The power MOSFET is the most widely used power device in the world.[4] Advantages over bipolar junction transistors in power electronics include MOSFETs not requiring a continuous flow of drive current to remain in the ON state, offering higher switching speeds, lower switching power losses, lower on-resistances, and reduced susceptibility to thermal runaway.[189] The power MOSFET had an impact on power supplies, enabling higher operating frequencies, size and weight reduction, and increased volume production.[190]

Switching power supplies are the most common applications for power MOSFETs.[52] They are also widely used for MOS RF power amplifiers, which enabled the transition of mobile networks from analog to digital in the 1990s. This led to the wide proliferation of wireless mobile networks, which revolutionised telecommunication systems.[178] The LDMOS in particular is the most widely used power amplifier in mobile networks, such as 2G, 3G,[178] 4G, and 5G.[179] Over 50 billion discrete power MOSFETs are shipped annually, as of 2018. They are widely used for automotive, industrial and communications systems in particular.[191] Power MOSFETs are commonly used in automotive electronics, particularly as switching devices in electronic control units,[192] and as power converters in modern electric vehicles.[193] The insulated-gate bipolar transistor (IGBT), a hybrid MOS-bipolar transistor, is also used for a wide variety of applications.[194]

Construction

Gate material

The primary criterion for the gate material is that it is a good conductor. Highly doped polycrystalline silicon is an acceptable but certainly not ideal conductor, and also suffers from some more technical deficiencies in its role as the standard gate material. Nevertheless, there are several reasons favoring use of polysilicon:

- The threshold voltage (and consequently the drain to source on-current) is modified by the work function difference between the gate material and channel material. Because polysilicon is a semiconductor, its work function can be modulated by adjusting the type and level of doping. Furthermore, because polysilicon has the same bandgap as the underlying silicon channel, it is quite straightforward to tune the work function to achieve low threshold voltages for both NMOS and PMOS devices. By contrast, the work functions of metals are not easily modulated, so tuning the work function to obtain low threshold voltages (LVT) becomes a significant challenge. Additionally, obtaining low-threshold devices on both PMOS and NMOS devices sometimes requires the use of different metals for each device type. While bimetallic integrated circuits (i.e., one type of metal for gate electrodes of NFETS and a second type of metal for gate electrodes of PFETS) are not common, they are known in patent literature and provide some benefit in terms of tuning electrical circuits' overall electrical performance.

- The silicon-SiO2 interface has been well studied and is known to have relatively few defects. By contrast many metal-insulator interfaces contain significant levels of defects which can lead to Fermi level pinning, charging, or other phenomena that ultimately degrade device performance.

- In the MOSFET IC fabrication process, it is preferable to deposit the gate material prior to certain high-temperature steps in order to make better-performing transistors. Such high temperature steps would melt some metals, limiting the types of metal that can be used in a metal-gate-based process.

While polysilicon gates have been the de facto standard for the last twenty years, they do have some disadvantages which have led to their likely future replacement by metal gates. These disadvantages include:

- Polysilicon is not a great conductor (approximately 1000 times more resistive than metals) which reduces the signal propagation speed through the material. The resistivity can be lowered by increasing the level of doping, but even highly doped polysilicon is not as conductive as most metals. To improve conductivity further, sometimes a high-temperature metal such as tungsten, titanium, cobalt, and more recently nickel is alloyed with the top layers of the polysilicon. Such a blended material is called silicide. The silicide-polysilicon combination has better electrical properties than polysilicon alone and still does not melt in subsequent processing. Also the threshold voltage is not significantly higher than with polysilicon alone, because the silicide material is not near the channel. The process in which silicide is formed on both the gate electrode and the source and drain regions is sometimes called salicide, self-aligned silicide.

- When the transistors are extremely scaled down, it is necessary to make the gate dielectric layer very thin, around 1 nm in state-of-the-art technologies. A phenomenon observed here is the so-called poly depletion, where a depletion layer is formed in the gate polysilicon layer next to the gate dielectric when the transistor is in the inversion. To avoid this problem, a metal gate is desired. A variety of metal gates such as tantalum, tungsten, tantalum nitride, and titanium nitride are used, usually in conjunction with high-κ dielectrics. An alternative is to use fully silicided polysilicon gates, a process known as FUSI.

Present high performance CPUs use metal gate technology, together with high-κ dielectrics, a combination known as high-κ, metal gate (HKMG). The disadvantages of metal gates are overcome by a few techniques:[195]

- The threshold voltage is tuned by including a thin "work function metal" layer between the high-κ dielectric and the main metal. This layer is thin enough that the total work function of the gate is influenced by both the main metal and thin metal work functions (either due to alloying during annealing, or simply due to the incomplete screening by the thin metal). The threshold voltage thus can be tuned by the thickness of the thin metal layer.

- High-κ dielectrics are now well studied, and their defects are understood.

- HKMG processes exist that do not require the metals to experience high temperature anneals; other processes select metals that can survive the annealing step.

Insulator

As devices are made smaller, insulating layers are made thinner, often through steps of thermal oxidation or localised oxidation of silicon (LOCOS). For nano-scaled devices, at some point tunneling of carriers through the insulator from the channel to the gate electrode takes place. To reduce the resulting leakage current, the insulator can be made thinner by choosing a material with a higher dielectric constant. To see how thickness and dielectric constant are related, note that Gauss's law connects field to charge as:

with Q = charge density, κ = dielectric constant, ε0 = permittivity of empty space and E = electric field. From this law it appears the same charge can be maintained in the channel at a lower field provided κ is increased. The voltage on the gate is given by:

with VG = gate voltage, Vch = voltage at channel side of insulator, and tins = insulator thickness. This equation shows the gate voltage will not increase when the insulator thickness increases, provided κ increases to keep tins / κ = constant (see the article on high-κ dielectrics for more detail, and the section in this article on gate-oxide leakage).

The insulator in a MOSFET is a dielectric which can in any event be silicon oxide, formed by LOCOS but many other dielectric materials are employed. The generic term for the dielectric is gate dielectric since the dielectric lies directly below the gate electrode and above the channel of the MOSFET.

Junction design

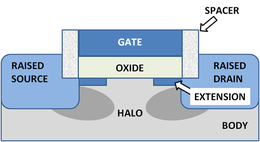

The source-to-body and drain-to-body junctions are the object of much attention because of three major factors: their design affects the current–voltage (I–V) characteristics of the device, lowering output resistance, and also the speed of the device through the loading effect of the junction capacitances, and finally, the component of stand-by power dissipation due to junction leakage.

The drain induced barrier lowering of the threshold voltage and channel length modulation effects upon I-V curves are reduced by using shallow junction extensions. In addition, halo doping can be used, that is, the addition of very thin heavily doped regions of the same doping type as the body tight against the junction walls to limit the extent of depletion regions.[196]

The capacitive effects are limited by using raised source and drain geometries that make most of the contact area border thick dielectric instead of silicon.[197]

These various features of junction design are shown (with artistic license) in the figure.

Scaling

| Semiconductor device fabrication |

|---|

|

(process nodes) |

|

Future

|

Over the past decades, the MOSFET (as used for digital logic) has continually been scaled down in size; typical MOSFET channel lengths were once several micrometres, but modern integrated circuits are incorporating MOSFETs with channel lengths of tens of nanometers. Robert Dennard's work on scaling theory was pivotal in recognising that this ongoing reduction was possible. The semiconductor industry maintains a "roadmap", the ITRS,[198] which sets the pace for MOSFET development. Historically, the difficulties with decreasing the size of the MOSFET have been associated with the semiconductor device fabrication process, the need to use very low voltages, and with poorer electrical performance necessitating circuit redesign and innovation (small MOSFETs exhibit higher leakage currents and lower output resistance). As of 2019, the smallest MOSFETs in production are 5 nm FinFET semiconductor nodes, manufactured by Samsung Electronics and TSMC.[199][200]

Smaller MOSFETs are desirable for several reasons. The main reason to make transistors smaller is to pack more and more devices in a given chip area. This results in a chip with the same functionality in a smaller area, or chips with more functionality in the same area. Since fabrication costs for a semiconductor wafer are relatively fixed, the cost per integrated circuits is mainly related to the number of chips that can be produced per wafer. Hence, smaller ICs allow more chips per wafer, reducing the price per chip. In fact, over the past 30 years the number of transistors per chip has been doubled every 2–3 years once a new technology node is introduced. For example, the number of MOSFETs in a microprocessor fabricated in a 45 nm technology can well be twice as many as in a 65 nm chip. This doubling of transistor density was first observed by Gordon Moore in 1965 and is commonly referred to as Moore's law.[201] It is also expected that smaller transistors switch faster. For example, one approach to size reduction is a scaling of the MOSFET that requires all device dimensions to reduce proportionally. The main device dimensions are the channel length, channel width, and oxide thickness. When they are scaled down by equal factors, the transistor channel resistance does not change, while gate capacitance is cut by that factor. Hence, the RC delay of the transistor scales with a similar factor. While this has been traditionally the case for the older technologies, for the state-of-the-art MOSFETs reduction of the transistor dimensions does not necessarily translate to higher chip speed because the delay due to interconnections is more significant.

Producing MOSFETs with channel lengths much smaller than a micrometre is a challenge, and the difficulties of semiconductor device fabrication are always a limiting factor in advancing integrated circuit technology. Though processes such as ALD have improved fabrication for small components, the small size of the MOSFET (less than a few tens of nanometers) has created operational problems:

- Higher subthreshold conduction

- As MOSFET geometries shrink, the voltage that can be applied to the gate must be reduced to maintain reliability. To maintain performance, the threshold voltage of the MOSFET has to be reduced as well. As threshold voltage is reduced, the transistor cannot be switched from complete turn-off to complete turn-on with the limited voltage swing available; the circuit design is a compromise between strong current in the on case and low current in the off case, and the application determines whether to favor one over the other. Subthreshold leakage (including subthreshold conduction, gate-oxide leakage and reverse-biased junction leakage), which was ignored in the past, now can consume upwards of half of the total power consumption of modern high-performance VLSI chips.[202][203]

- Increased gate-oxide leakage