AMD Eyefinity

AMD Eyefinity is a brand name for AMD video card products that support multi-monitor setups by integrating multiple (up to six) display controllers on one GPU.[1] AMD Eyefinity was introduced with the Radeon HD 5000 Series "Evergreen" in September 2009 and has been available on APUs and professional-grade graphics cards branded AMD FirePro as well.[2]

| |

| Design firm | Advanced Micro Devices |

|---|---|

| Introduced | September 2009 |

| Type | multi-monitor or video walls |

| Ports | DisplayPort, HDMI, DVI, VGA, DMS-59, VHDCI |

AMD Eyefinity supports a maximum of 2 non-DisplayPort displays (e.g., HDMI, DVI, VGA, DMS-59, VHDCI) (which AMD calls "legacy output") and up to 6 DisplayPort displays simultaneously using a single graphics card or APU. To feed more than two displays, the additional panels must have native DisplayPort support.[3] Alternatively active DisplayPort-to-DVI/HDMI/VGA adapters can be employed.[4]

The setup of large video walls by connecting multiple computers over Gigabit Ethernet or Ethernet is also supported.[5]

The version of AMD Eyefinity (aka DCE, display controller engine) introduced with Excavator-based Carrizo APUs features a Video underlay pipe.[6]

Overview

AMD Eyefinity is implemented by multiple on-die display controllers. The 5000-series designs host two internal clocks and one external clock. Displays connected over VGA, DVI, or HDMI each require their own internal clock. But all displays connected over DisplayPort can be driven from only one external clock. This external clock is what allows Eyefinity to fuel up to six monitors from a single card.

The entire HD 5000 series of products have Eyefinity capabilities supporting three outputs. The Radeon HD 5870 Eyefinity Edition, however, supports six mini DisplayPort outputs, all of which can be simultaneously active.[7]

The display controller has two RAMDACs that drive the VGA or DVI ports in analog mode. For example, when a DVI-to-VGA converter is attached to a DVI port). It also has a maximum of six digital transmitters that can output either a DisplayPort signal or a TMDS signal for either DVI or HDMI, and two clock signal generators to drive the digital outputs in TMDS mode. Dual-link DVI displays use two of the TMDS/DisplayPort transmitters and one clock signal each. Single-link DVI displays and HDMI displays use one TMDS/DisplayPort transmitter and one clock signal each. DisplayPort displays use one TMDS/DisplayPort transmitter and no clock signal.

An active DisplayPort adapter can convert a DisplayPort signal to another type of signal—like VGA, single-link DVI, or dual-link DVI; or HDMI if more than two non-DisplayPort displays must be connected to a Radeon HD 5000 series graphics card.[7]

DisplayPort 1.2 added the possibility to drive multiple displays on single DisplayPort connector, called Multi-Stream Transport (MST). AMD graphics solutions equipped with DisplayPort 1.2 outputs can run multiple monitors from a single port.

At High-Performance Graphics 2010 Mark Fowler presented the Evergreen and stated that e.g. 5870 (Cypress), 5770 (Juniper) and 5670 (Redwood) support max resolution of the 6 times 2560×1600 pixels, while the 5470 (Cedar) supports 4 times 2560×1600 pixels.[8]

Availability

Feature overview for AMD graphics cards

All AMD GPUs starting with the Evergreen series support a maximum of 2 non-DisplayPort displays and a maximum of 6 DisplayPort displays per graphics card.[4]

The following table shows features of AMD's GPUs (see also: List of AMD graphics processing units).

| Name of GPU series | Wonder | Mach | 3D Rage | Rage Pro | Rage | R100 | R200 | R300 | R400 | R500 | R600 | RV670 | R700 | Evergreen | Northern Islands |

Southern Islands |

Sea Islands |

Volcanic Islands |

Arctic Islands/Polaris |

Vega | Navi |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Released | 1986 | 1991 | 1996 | 1997 | 1998 | Apr 2000 | Aug 2001 | Sep 2002 | May 2004 | Oct 2005 | May 2007 | Nov 2007 | Jun 2008 | Sep 2009 | Oct 2010 | Jan 2012 | Sep 2013 | Jun 2015 | Jun 2016 | Jun 2017 | Jul 2019 |

| Marketing Name | Wonder | Mach | 3D Rage | Rage Pro | Rage | Radeon 7000 | Radeon 8000 | Radeon 9000 | Radeon X700/X800 | Radeon X1000 | Radeon HD 1000/2000 | Radeon HD 3000 | Radeon HD 4000 | Radeon HD 5000 | Radeon HD 6000 | Radeon HD 7000 | Radeon Rx 200 | Radeon Rx 300 | Radeon RX 400/500 | Radeon RX Vega/Radeon VII(7nm) | Radeon RX 5000 |

| AMD support | |||||||||||||||||||||

| Kind | 2D | 3D | |||||||||||||||||||

| Instruction set | Not publicly known | TeraScale instruction set | GCN instruction set | RDNA instruction set | |||||||||||||||||

| Microarchitecture | TeraScale 1 | TeraScale 2 (VLIW5) | TeraScale 3 (VLIW4) | GCN 1st gen | GCN 2nd gen | GCN 3rd gen | GCN 4th gen | GCN 5th gen | RDNA | ||||||||||||

| Type | Fixed pipeline[lower-alpha 1] | Programmable pixel & vertex pipelines | Unified shader model | ||||||||||||||||||

| Direct3D | N/A | 5.0 | 6.0 | 7.0 | 8.1 | 9.0 11 (9_2) |

9.0b 11 (9_2) |

9.0c 11 (9_3) |

10.0 11 (10_0) |

10.1 11 (10_1) |

11 (11_0) | 11 (11_1) 12 (11_1) |

11 (12_0) 12 (12_0) |

11 (12_1) 12 (12_1) | |||||||

| Shader model | N/A | 1.4 | 2.0+ | 2.0b | 3.0 | 4.0 | 4.1 | 5.0 | 5.1 | 5.1 6.3 |

6.4 | ||||||||||

| OpenGL | N/A | 1.1 | 1.2 | 1.3 | 2.0[lower-alpha 2] | 3.3 | 4.5 (on Linux + Mesa 3D: 4.2 with FP64 HW support, 3.3 without)[9][10][11][lower-alpha 3] | 4.6 (on Linux: 4.6 (Mesa 20.0)) | |||||||||||||

| Vulkan | N/A | 1.0 (Win 7+ or Mesa 17+) |

1.2 (Adrenalin 20.1, Linux Mesa 20.0) | ||||||||||||||||||

| OpenCL | N/A | Close to Metal | 1.1 | 1.2 | 2.0 (Adrenalin driver on Win7+) (1.2 on Linux, 2.1 with AMD ROCm) |

? | |||||||||||||||

| HSA | N/A | ? | |||||||||||||||||||

| Video decoding ASIC | N/A | Avivo/UVD | UVD+ | UVD 2 | UVD 2.2 | UVD 3 | UVD 4 | UVD 4.2 | UVD 5.0 or 6.0 | UVD 6.3 | UVD 7[12][lower-alpha 4] | VCN 2.0[12][lower-alpha 4] | |||||||||

| Video encoding ASIC | N/A | VCE 1.0 | VCE 2.0 | VCE 3.0 or 3.1 | VCE 3.4 | VCE 4.0[12][lower-alpha 4] | |||||||||||||||

| Power saving | ? | PowerPlay | PowerTune | PowerTune & ZeroCore Power | ? | ||||||||||||||||

| TrueAudio | N/A | Via dedicated DSP | Via shaders | ||||||||||||||||||

| FreeSync | N/A | 1 2 | |||||||||||||||||||

| HDCP[lower-alpha 5] | ? | 1.4 | 1.4 2.2 |

1.4 2.2 2.3 | |||||||||||||||||

| PlayReady[lower-alpha 5] | N/A | 3.0 | 3.0 | ||||||||||||||||||

| Supported displays[lower-alpha 6] | 1–2 | 2 | 2–6 | ? | |||||||||||||||||

| Max. resolution | ? | 2–6 × 2560×1600 |

2–6 × 4096×2160 @ 60 Hz |

2–6 × 5120×2880 @ 60 Hz |

3 × 7680×4320 @ 60 Hz[13] |

? | |||||||||||||||

/drm/radeon[lower-alpha 7] |

N/A | ||||||||||||||||||||

/drm/amdgpu[lower-alpha 7] |

N/A | Experimental[14] | |||||||||||||||||||

- The Radeon 100 Series has programmable pixel shaders, but do not fully comply with DirectX 8 or Pixel Shader 1.0. See article on R100's pixel shaders.

- These series do not fully comply with OpenGL 2+ as the hardware does not support all types of non-power of two (NPOT) textures.

- OpenGL 4+ compliance requires supporting FP64 shaders and these are emulated on some TeraScale chips using 32-bit hardware.

- The UVD and VCE were replaced by the Video Core Next (VCN) ASIC in the Raven Ridge APU implementation of Vega.

- To play protected video content, it also requires card, operating system, driver, and application support. A compatible HDCP display is also needed for this. HDCP is mandatory for the output of certain audio formats, placing additional constraints on the multimedia setup.

- More displays may be supported with native DisplayPort connections, or splitting the maximum resolution between multiple monitors with active converters.

- DRM (Direct Rendering Manager) is a component of the Linux kernel. Support in this table refers to the most current version.

Feature overview for AMD APUs

AMD Eyefinity is also available in AMD's APU branded product line. The A10-7850K is said to support up to four displays.

The following table shows features of AMD's APUs (see also: List of AMD accelerated processing units).

| Codename | Server | Basic | Toronto | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Micro | Kyoto | |||||||||||||||||

| Desktop | Mainstream | Carrizo | Bristol Ridge | Raven Ridge | Picasso | Renoir | ||||||||||||

| Entry | Llano | Trinity | Richland | Kaveri | ||||||||||||||

| Basic | Kabini | |||||||||||||||||

| Mobile | Performance | Renoir | ||||||||||||||||

| Mainstream | Llano | Trinity | Richland | Kaveri | Carrizo | Bristol Ridge | Raven Ridge | Picasso | ||||||||||

| Entry | Dalí | |||||||||||||||||

| Basic | Desna, Ontario, Zacate | Kabini, Temash | Beema, Mullins | Carrizo-L | Stoney Ridge | |||||||||||||

| Embedded | Trinity | Bald Eagle | Merlin Falcon, Brown Falcon |

Great Horned Owl | Ontario, Zacate | Kabini | Steppe Eagle, Crowned Eagle, LX-Family |

Prairie Falcon | Banded Kestrel | |||||||||

| Platform | High, standard and low power | Low and ultra-low power | ||||||||||||||||

| Released | Aug 2011 | Oct 2012 | Jun 2013 | Jan 2014 | Jun 2015 | Jun 2016 | Oct 2017 | Jan 2019 | Mar 2020 | Jan 2011 | May 2013 | Apr 2014 | May 2015 | Feb 2016 | Apr 2019 | |||

| CPU microarchitecture | K10 | Piledriver | Steamroller | Excavator | "Excavator+"[15] | Zen | Zen+ | Zen 2 | Bobcat | Jaguar | Puma | Puma+[16] | "Excavator+" | Zen | ||||

| ISA | x86-64 | x86-64 | ||||||||||||||||

| Socket | Desktop | High-end | N/A | N/A | ||||||||||||||

| Mainstream | N/A | AM4 | ||||||||||||||||

| Entry | FM1 | FM2 | FM2+[lower-alpha 1] | N/A | ||||||||||||||

| Basic | N/A | N/A | AM1 | N/A | ||||||||||||||

| Other | FS1 | FS1+, FP2 | FP3 | FP4 | FP5 | FP6 | FT1 | FT3 | FT3b | FP4 | FP5 | |||||||

| PCI Express version | 2.0 | 3.0 | 4.0 | 2.0 | 3.0 | |||||||||||||

| Fab. (nm) | GF 32SHP (HKMG SOI) |

GF 28SHP (HKMG bulk) |

GF 14LPP (FinFET bulk) |

GF 12LP (FinFET bulk) |

TSMC N7 (FinFET bulk) |

TSMC N40 (bulk) |

TSMC N28 (HKMG bulk) |

GF 28SHP (HKMG bulk) |

GF 14LPP (FinFET bulk) | |||||||||

| Die area (mm2) | 228 | 246 | 245 | 245 | 250 | 210[17] | 156 | 75 (+ 28 FCH) | 107 | ? | 125 | 149 | ||||||

| Min TDP (W) | 35 | 17 | 12 | 10 | 4.5 | 4 | 3.95 | 10 | 6 | |||||||||

| Max APU TDP (W) | 100 | 95 | 65 | 18 | 25 | |||||||||||||

| Max stock APU base clock (GHz) | 3 | 3.8 | 4.1 | 3.7 | 3.8 | 3.6 | 3.7 | 3.8 | 1.75 | 2.2 | 2 | 2.2 | 3.2 | 3.3 | ||||

| Max APUs per node[lower-alpha 2] | 1 | 1 | ||||||||||||||||

| Max CPU[lower-alpha 3] cores per APU | 4 | 8 | 2 | 4 | 2 | |||||||||||||

| Max threads per CPU core | 1 | 2 | 1 | 2 | ||||||||||||||

| Integer structure | 3+3 | 2+2 | 4+2 | 4+2+1 | 1+1+1+1 | 2+2 | 4+2 | |||||||||||

| i386, i486, i586, CMOV, NOPL, i686, PAE, NX bit, CMPXCHG16B, AMD-V, RVI, ABM, and 64-bit LAHF/SAHF | ||||||||||||||||||

| IOMMU[lower-alpha 4] | N/A | |||||||||||||||||

| BMI1, AES-NI, CLMUL, and F16C | N/A | |||||||||||||||||

| MOVBE | N/A | |||||||||||||||||

| AVIC, BMI2 and RDRAND | N/A | |||||||||||||||||

| ADX, SHA, RDSEED, SMAP, SMEP, XSAVEC, XSAVES, XRSTORS, CLFLUSHOPT, and CLZERO | N/A | N/A | ||||||||||||||||

| WBNOINVD, CLWB, RDPID, RDPRU, and MCOMMIT | N/A | N/A | ||||||||||||||||

| FPUs per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||

| Pipes per FPU | 2 | 2 | ||||||||||||||||

| FPU pipe width | 128-bit | 256-bit | 80-bit | 128-bit | ||||||||||||||

| CPU instruction set SIMD level | SSE4a[lower-alpha 5] | AVX | AVX2 | SSSE3 | AVX | AVX2 | ||||||||||||

| 3DNow! | 3DNow!+ | N/A | N/A | |||||||||||||||

| PREFETCH/PREFETCHW | ||||||||||||||||||

| FMA4, LWP, TBM, and XOP | N/A | N/A | N/A | N/A | ||||||||||||||

| FMA3 | ||||||||||||||||||

| L1 data cache per core (KiB) | 64 | 16 | 32 | 32 | ||||||||||||||

| L1 data cache associativity (ways) | 2 | 4 | 8 | 8 | ||||||||||||||

| L1 instruction caches per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||

| Max APU total L1 instruction cache (KiB) | 256 | 128 | 192 | 256 | 512 | 64 | 128 | 96 | 128 | |||||||||

| L1 instruction cache associativity (ways) | 2 | 3 | 4 | 8 | 2 | 3 | 4 | |||||||||||

| L2 caches per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | ||||||||||||

| Max APU total L2 cache (MiB) | 4 | 2 | 4 | 1 | 2 | 1 | ||||||||||||

| L2 cache associativity (ways) | 16 | 8 | 16 | 8 | ||||||||||||||

| APU total L3 cache (MiB) | N/A | 4 | 8 | N/A | 4 | |||||||||||||

| APU L3 cache associativity (ways) | 16 | 16 | ||||||||||||||||

| L3 cache scheme | Victim | N/A | Victim | Victim | ||||||||||||||

| Max stock DRAM support | DDR3-1866 | DDR3-2133 | DDR3-2133, DDR4-2400 | DDR4-2400 | DDR4-2933 | DDR4-3200, LPDDR4-4266 | DDR3L-1333 | DDR3L-1600 | DDR3L-1866 | DDR3-1866, DDR4-2400 | DDR4-2400 | |||||||

| Max DRAM channels per APU | 2 | 1 | 2 | |||||||||||||||

| Max stock DRAM bandwidth (GB/s) per APU | 29.866 | 34.132 | 38.400 | 46.932 | 68.256 | 10.666 | 12.800 | 14.933 | 19.200 | 38.400 | ||||||||

| GPU microarchitecture | TeraScale 2 (VLIW5) | TeraScale 3 (VLIW4) | GCN 2nd gen | GCN 3rd gen | GCN 5th gen[18] | TeraScale 2 (VLIW5) | GCN 2nd gen | GCN 3rd gen[18] | GCN 5th gen | |||||||||

| GPU instruction set | TeraScale instruction set | GCN instruction set | TeraScale instruction set | GCN instruction set | ||||||||||||||

| Max stock GPU base clock (MHz) | 600 | 800 | 844 | 866 | 1108 | 1250 | 1400 | 2100 | 538 | 600 | ? | 847 | 900 | 1200 | ||||

| Max stock GPU base GFLOPS[lower-alpha 6] | 480 | 614.4 | 648.1 | 886.7 | 1134.5 | 1760 | 1971.2 | 2150.4 | 86 | ? | ? | ? | 345.6 | 460.8 | ||||

| 3D engine[lower-alpha 7] | Up to 400:20:8 | Up to 384:24:6 | Up to 512:32:8 | Up to 704:44:16[19] | Up to 512:?:? | 80:8:4 | 128:8:4 | Up to 192:?:? | Up to 192:?:? | |||||||||

| IOMMUv1 | IOMMUv2 | IOMMUv1 | ? | IOMMUv2 | ||||||||||||||

| Video decoder | UVD 3.0 | UVD 4.2 | UVD 6.0 | VCN 1.0[20] | UVD 3.0 | UVD 4.0 | UVD 4.2 | UVD 6.0 | UVD 6.3 | VCN 1.0 | ||||||||

| Video encoder | N/A | VCE 1.0 | VCE 2.0 | VCE 3.1 | N/A | VCE 2.0 | VCE 3.1 | |||||||||||

| GPU power saving | PowerPlay | PowerTune | PowerPlay | PowerTune[21] | ||||||||||||||

| TrueAudio | N/A | N/A | ||||||||||||||||

| FreeSync | 1 2 | 1 2 | ||||||||||||||||

| HDCP[lower-alpha 8] | ? | 1.4 | 1.4 2.2 | ? | 1.4 | 1.4 2.2 | ||||||||||||

| PlayReady[lower-alpha 8] | N/A | 3.0 not yet | N/A | 3.0 not yet | ||||||||||||||

| Supported displays[lower-alpha 9] | 2–3 | 2–4 | 3 | 3 (desktop) 4 (mobile, embedded) | 4 | 2 | 3 | 4 | ||||||||||

/drm/radeon[lower-alpha 10][24][4] | N/A | N/A | ||||||||||||||||

/drm/amdgpu[lower-alpha 10][25] | N/A | N/A | ||||||||||||||||

- APU models: A8-7680, A6-7480. CPU only: Athlon X4 845.

- A PC would be one node.

- An APU combines a CPU and a GPU. Both have cores.

- Requires firmware support.

- No SSE4. No SSSE3.

- Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

- Unified shaders : texture mapping units : render output units

- To play protected video content, it also requires card, operating system, driver, and application support. A compatible HDCP display is also needed for this. HDCP is mandatory for the output of certain audio formats, placing additional constraints on the multimedia setup.

- To feed more than two displays, the additional panels must have native DisplayPort support.[23] Alternatively active DisplayPort-to-DVI/HDMI/VGA adapters can be employed.

- DRM (Direct Rendering Manager) is a component of the Linux kernel. Support in this table refers to the most current version.

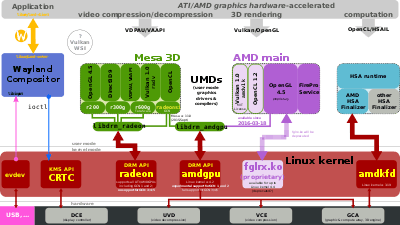

Software support

AMD Catalyst supports Eyefinity and enables the user to independently configure and run each attached displays. It facilitates the configuration of "cloned mode", i.e. to copy one desktop onto multiple screens or "extended mode", i.e. to span the workspace across multiple screens and combine the resolutions of all of those displays into one big resolution. AMD calls the extended modes Single Large Surface (SLS) and Catalyst support of certain range of display group configurations. For example, 5x1 landscape and 5x1 portrait are supported since AMD Catalyst version 11.10 from October 2011.[2][27]

Starting in Catalyst 14.6, AMD supports mixed resolution support, so a single Eyefinity display group can drive each monitor at a different resolution. This is provided through two new Eyefinity display modes, Fit and Expand, in addition to the existing Fill mode. In Fit or Expand mode, AMD compensates for mismatched resolutions by creating a virtual desktop of a different resolution than the monitors, and then either padding it out or cropping it as is necessary.[28]

AMD Eyefinity works with games that support non-standard aspect ratios, which is required for panning across multiple displays. SLS ("Single Large Surface") mode requires an identical display resolution on all configured displays. AMD validated some video games to support Eyefinity. The short list includes titles such as Age of Conan, ARMA 2: Operation Arrowhead, S.T.A.L.K.E.R.: Call of Pripyat, Serious Sam 3: BFE, Singularity (video game), Sleeping Dogs, Assassin's Creed II, Sniper Elite V2, Soldier of Fortune Online, Tom Clancy's Splinter Cell: Conviction, Star Wars: The Force Unleashed 2, Marvel Super Hero Squad Online, R.U.S.E., Supreme Commander 2 among others.[29] However, some games not on this short list seem to work as well, e.g. Dirt 3 and The Elder Scrolls V: Skyrim.

KMS driver supports AMD Eyefinity.[4]

See also

| Wikimedia Commons has media related to AMD Eyefinity. |

- AMD FireMV – pre-Eyefinity products for multi-monitor set-ups

- Multi-monitor

References

- "AMD's Radeon HD 5870 Eyefinity 6 Edition Reviewed". AnandTech. 2010-03-31. Retrieved 2014-07-02.

- "AMD Eyefinity: FAQ". AMD. 2011-05-17. Retrieved 2014-07-02.

- "How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?". AMD. Retrieved 2014-12-08.

- "Radeon feature matrix". freedesktop.org. Retrieved 10 January 2016.

- "Configuring and Running a Large Video Wall using ATI FirePro Graphics" (pdf). Retrieved 2014-07-04.

- "Carrizo introduces a new video playback pathways".

- "AMD Eyefinity on AMD Radeon HD 5870". Tom's Hardware. 2009-09-23. Retrieved 2014-07-02.

- "Presenting Radeon HD 5000" (PDF).

- "AMD Radeon Software Crimson Edition Beta". AMD. Retrieved 2018-04-20.

- "Mesamatrix". mesamatrix.net. Retrieved 2018-04-22.

- "RadeonFeature". X.Org Foundation. Retrieved 2018-04-20.

- Killian, Zak (22 March 2017). "AMD publishes patches for Vega support on Linux". Tech Report. Retrieved 23 March 2017.

- "Radeon's next-generation Vega architecture" (PDF). Radeon Technologies Group (AMD). Archived from the original (PDF) on 2018-09-06. Retrieved 13 June 2017.

- Larabel, Michael (7 December 2016). "The Best Features of the Linux 4.9 Kernel". Phoronix. Retrieved 7 December 2016.

- "AMD Announces the 7th Generation APU: Excavator mk2 in Bristol Ridge and Stoney Ridge for Notebooks". 31 May 2016. Retrieved 3 January 2020.

- "AMD Mobile "Carrizo" Family of APUs Designed to Deliver Significant Leap in Performance, Energy Efficiency in 2015" (Press release). 20 November 2014. Retrieved 16 February 2015.

- "The Mobile CPU Comparison Guide Rev. 13.0 Page 5 : AMD Mobile CPU Full List". TechARP.com. Retrieved 13 December 2017.

- "AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver". VideoCardz.com. Retrieved 6 June 2017.

- Cutress, Ian (1 February 2018). "Zen Cores and Vega: Ryzen APUs for AM4 – AMD Tech Day at CES: 2018 Roadmap Revealed, with Ryzen APUs, Zen+ on 12nm, Vega on 7nm". Anandtech. Retrieved 7 February 2018.

- Larabel, Michael (17 November 2017). "Radeon VCN Encode Support Lands in Mesa 17.4 Git". Phoronix. Retrieved 20 November 2017.

- Tony Chen; Jason Greaves, "AMD's Graphics Core Next (GCN) Architecture" (PDF), AMD, retrieved 13 August 2016

- "A technical look at AMD's Kaveri architecture". Semi Accurate. Retrieved 6 July 2014.

- "How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?". AMD. Retrieved 8 December 2014.

- Airlie, David (26 November 2009). "DisplayPort supported by KMS driver mainlined into Linux kernel 2.6.33". Retrieved 16 January 2016.

- Deucher, Alexander (16 September 2015). "XDC2015: AMDGPU" (PDF). Retrieved 16 January 2016.

- Michel Dänzer (17 November 2016). "[ANNOUNCE] xf86-video-amdgpu 1.2.0". lists.x.org.

- "AMD's Eyefinity Technology Explained". Tom's Hardware. 2010-02-28. Retrieved 2014-07-02.

- "AMD Catalyst 14.6 beta adds new Eyefinity functionality". AnandTech. 2014-05-27. Retrieved 2014-07-02.

- "AMD Eyefinity Validated and Ready Software".