Cypress PSoC

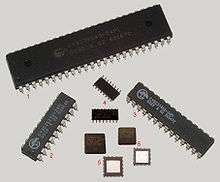

PSoC (programmable system on a chip) is a family of microcontroller integrated circuits by Cypress Semiconductor. These chips include a CPU core and mixed-signal arrays of configurable integrated analog and digital peripherals.

History

In 2002, Cypress began shipping commercial quantities of the PSoC 1.[1] To promote the PSoC, Cypress sponsored a "PSoC Design Challenge" in Circuit Cellar magazine in 2002 and 2004.[2]

In April 2013, Cypress released the fourth generation, PSoC 4. The PSoC 4 features a 32-bit ARM Cortex-M0 CPU, with programmable analog blocks (operational amplifiers and comparators), programmable digital blocks (PLD-based UDBs), programmable routing and flexible GPIO (route any function to any pin), a serial communication block (for SPI, UART, I²C), a timer/counter/PWM block and more.[3]

PSoC is used in devices as simple as Sonicare toothbrushes and Adidas sneakers, and as complex as the TiVo set-top box. One PSoC, using CapSense, controls the touch-sensitive scroll wheel on the Apple iPod click wheel.

In 2014, Cypress extended the PSoC 4 family by integrating a Bluetooth Low Energy radio along with a PSoC 4 Cortex-M0-based SoC in a single, monolithic die.

In 2016, Cypress released PSoC 4 S-Series, featuring ARM Cortex-M0+ CPU.[4]

Overview

A PSoC integrated circuit is composed of a core, configurable analog and digital blocks, and programmable routing and interconnect. The configurable blocks in a PSoC are the biggest difference from other microcontrollers.

PSoC has three separate memory spaces: paged SRAM for data, Flash memory for instructions and fixed data, and I/O registers for controlling and accessing the configurable logic blocks and functions. The device is created using SONOS technology.

PSoC resembles an ASIC: blocks can be assigned a wide range of functions and interconnected on-chip. Unlike an ASIC, there is no special manufacturing process required to create the custom configuration — only startup code that is created by Cypress' PSoC Designer (for PSoC 1) or PSoC Creator (for PSoC 3 / 4 / 5) IDE.

PSoC resembles an FPGA in that at power up it must be configured, but this configuration occurs by loading instructions from the built-in Flash memory.

PSoC most closely resembles a microcontroller combined with a PLD and programmable analog. Code is executed to interact with the user-specified peripheral functions (called "Components"), using automatically generated APIs and interrupt routines. PSoC Designer or PSoC Creator generate the startup configuration code. Both integrate APIs that initialize the user selected components upon the users needs in a Visual-Studio-like GUI.

Configurable analog and digital blocks

Using configurable analog and digital blocks, designers can create and change mixed-signal embedded applications. The digital blocks are state machines that are configured using the blocks registers. There are two types of digital blocks, Digital Building Blocks (DBBxx) and Digital Communication Blocks (DCBxx). Only the communication blocks can contain serial I/O user modules, such as SPI, UART, etc.

Each digital block is considered an 8-bit resource that designers can configure using pre-built digital functions or user modules (UM), or, by combining blocks, turn them into 16-, 24-, or 32-bit resources. Concatenating UMs together is how 16-bit PWMs and timers are created.

There are two types of analog blocks. The continuous time (CT) blocks are composed of an op-amp circuit and designated as ACBxx where xx is 00–03. The other type is the switch cap (SC) blocks, which allow complex analog signal flows and are designated by ASCxy where x is the row and y is the column of the analog block. Designers can modify and personalize each module to any design.

Programmable routing and interconnect

PSoC mixed-signal arrays' flexible routing allows designers to route signals to and from I/O pins more freely than with many competing microcontrollers. Global buses allow for signal multiplexing and for performing logic operations. Cypress suggests that this allows designers to configure a design and make improvements more easily and faster and with fewer PCB redesigns than a digital logic gate approach or competing microcontrollers with more fixed function pins.

Series

There are five different families of devices, each based around a different microcontroller core:

- PSoC 1 — CY8C2xxxx series — M8C core.

- PSoC 3 — CY8C3xxxx series — 8051 core.

- PSoC 4 — CY8C4xxxx series — ARM Cortex-M0 core.[5]

- PSoC 5/5LP — CY8C5xxxx series — ARM Cortex-M3 core.

- PSoC 6 — CY8C6xxxx series — ARM Cortex-M4 core with an added ARM Cortex-M0+ core (in some models).[6]

- Bluetooth Low Energy

Starting in 2014, Cypress began offering PSoC 4 BLE devices with integrated Bluetooth Low Energy (Bluetooth Smart). This can be used to create connected products leveraging the analog and digital blocks.[7] Users can add and configure the BLE module directly in PSoC creator. Cypress also provides a complete Bluetooth Low Energy stack licensed from Mindtree with both Peripheral and Central functionality.[8] The PSoC 6 series includes versions with BLE including Bluetooth 5 features including extended range or higher speed.

Summary

| PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5/5LP | PSoC 6 |

|---|---|---|---|---|

| 8-bit M8C core up to 24 MHz, 4 MIPS |

8-bit 8051 core (single-cycle) up to 67 MHz, 33 MIPS |

32-bit ARM Cortex-M0 up to 48 MHz, ? MIPS |

32-bit ARM Cortex-M3 up to 80 MHz, 84 MIPS |

32-bit ARM Cortex-M4 (up to 150 MHz) 32-bit ARM Cortex-M0+ (opt. up to 100 MHz) |

| Flash: 4 KB to 32 KB SRAM: 256 bytes to 2 KB |

Flash: 8 KB to 64 KB SRAM: 3 KB to 8 KB |

Flash: 16 KB to 256 KB SRAM: 2 KB to 32 KB |

Flash: 32 KB to 256 KB SRAM: 8 KB to 64 KB |

Flash: 512 KB to 2048 KB SRAM: 128 KB to 512 KB expandable using quad SPI |

| I²C, SPI, UART, FS USB 2.0 |

I²C, SPI, UART, LIN, FS USB 2.0, I²S, CAN |

I²C, SPI, UART, CAN . |

I²C, SPI, UART, LIN, CAN,

FS USB 2.0, I²S |

I²C, SPI, UART, LIN, BLE (opt.), FS USB 2.0 (opt. host & device) |

| 16 digital PSoC blocks | 16 to 24 UDBs (Universal Digital Blocks) | 4 to 8 UDBs | 20 to 24 UDBs | 0 to 12 UDBs |

| 1 Delta-Sigma ADC (6 to 14-bit)

131 ksps @ 8-bit; 1 Sigma-Delta ADC (for capacitive sensing) Up to two DACs (6 to 8-bit) |

1 Delta-Sigma ADC (8 to 20-bit)

192 ksps @ 12-bit; Up to four DACs (8-bit) |

1 SAR ADC (12-bit)

1 Msps @ 12-bit; Up to two DACs (7 to 8-bit) |

1 Delta-Sigma ADC (8 to 20-bit)

192 ksps @12-bit; 2 SAR ADCs (12-bit) 1 Msps @ 12-bit; Up to four DACs (8-bit) |

1 SAR ADC (12-bit) 1 MSPS

1 12 Bit Voltage Mode DAC |

| Up to 64 I/O | Up to 72 I/O | Up to 98 I/O | Up to 72 I/O | Up to 104 I/O |

| Operation: 1.7 V to 5.25 V Active: 2 mA, Sleep: 3 μA Hibernate: ? |

Operation: 0.5 V to 5.5 V Active: 1.2 mA, Sleep: 1 μA, Hibernate: 200 nA |

Operation: 1.71 V to 5.5 V Active: 1.6 mA, Sleep: 1.3 μA, Hibernate: 150 nA |

Operation: 2.7 V to 5.5 V Active: 2 mA, Sleep: 2 μA, Hibernate: 300 nA |

|

| Requires ICE Cube and FlexPods | On-chip SWD, Debug | On-chip JTAG, SWD, SWV, Debug, Trace |

||

| CY8CKIT-001 Development Kit | CY8CKIT-001 Development Kit CY8CKIT-030 Development Kit |

CY8CKIT-040 4000 Pioneer Kit CY8CKIT-042 4200 Pioneer Kit CY8CKIT-043 4200M Prototyping Kit CY8CKIT-044 4200M Pioneer Kit CY8CKIT-046 4200L Pioneer Kit |

CY8CKIT-001 Development Kit CY8CKIT-050 Development Kit CY8CKIT-059 Prototype Kit |

CY8CKIT-062-BLE Pioneer Kit |

Development tools

PSoC Designer

This is the first generation software IDE to design and debug and program the PSoC 1 devices. It introduced unique features including a library of pre-characterized analog and digital peripherals in a drag-and-drop design environment which could then be customized to specific design needs by leveraging the dynamically generated API libraries of code.

PSoC Creator

PSoC Creator is the second generation software IDE to design debug and program the PSoC 3 / 4 / 5 devices. The development IDE is combined with an easy to use graphical design editor to form a powerful hardware/software co-design environment. PSoC Creator consists of two basic building blocks. The program that allows the user to select, configure and connect existing circuits on the chip and the components which are the equivalent of peripherals on MCUs. What makes PSoC intriguing is the possibility to create own application specific peripherals in hardware. Cypress publishes component packs several times a year. PSoC users get new peripherals for their existing hardware without being charged or having to buy new hardware. PSoC Creator also allows much freedom in assignment of peripherals to I/O pins.

Cortex-M

Generic ARM development tools for PSoC 4 and PSoC 5.

Documentation

- PSoC 4 / 5

The amount of documentation for all ARM chips is daunting, especially for newcomers. The documentation for microcontrollers from past decades would easily be inclusive in a single document, but as chips have evolved so has the documentation grown. The total documentation is especially hard to grasp for all ARM chips since it consists of documents from the IC manufacturer (Cypress Semiconductor) and documents from CPU core vendor (ARM Holdings).

A typical top-down documentation tree is: manufacturer website, manufacturer marketing slides, manufacturer datasheet for the exact physical chip, manufacturer detailed reference manual that describes common peripherals and aspects of a physical chip family, ARM core generic user guide, ARM core technical reference manual, ARM architecture reference manual that describes the instruction set(s).

- PSoC 4 / 5 documentation tree (top to bottom)

- PSoC website.

- PSoC marketing slides.

- PSoC datasheet.

- PSoC reference manuals.

- ARM core website.

- ARM core generic user guide.

- ARM core technical reference manual.

- ARM architecture reference manual.

Cypress Semiconductor has additional documents, such as: evaluation board user manuals, application notes, getting started guides, software library documents, errata, and more. See External Links section for links to official PSoC and ARM documents.

See also

- ARM architecture, List of ARM microprocessor cores, ARM Cortex-M

- Microcontroller, (List of common microcontrollers)

- Embedded systems

- Single-board microcontroller

- Interrupt, Interrupt handler, Comparison of real-time operating systems

- Joint Test Action Group

- Serial Wire Debug

- Field-programmable analog array

- Reconfigurable computing

References

- Reuters: "Cypress Hits Half-Billion Mark in Shipments of PSoC Programmable system on a chip Devices" 2009

- Circuit Cellar:"PSoC Design Challenge 2002" Archived 2009-07-03 at the Wayback Machine

- "Fully Qualified Production Silicon for Cypress's First Two PSoC® 4 Product Families Is Now Available". yahoo.com. Retrieved April 12, 2018.

- Corp., Cypress Semiconductor. "Cypress Offers Complete Portfolio of Flexible PSoC ARM Cortex-M0 and Cortex-M0+ Solutions to Replace Legacy 8-Bit and 16-Bit Platforms". www.prnewswire.com. Retrieved March 4, 2016.

- "Custom Peripherals Surround Cortex-M0 Platform".

- "PSoC 6 CY8CKIT-062 Pioneer Kit - Cypress - DigiKey". www.digikey.com. Retrieved April 12, 2018.

- "PSoC® 4 BLE (Bluetooth Smart)". Retrieved February 12, 2015.

- "Cypress offering BLE chipset, Here's what you need to know". Retrieved February 12, 2015.

Further reading

External links

| Wikimedia Commons has media related to Cypress PSoC. |

| Wikibooks has a book on the topic of: Embedded Systems/Cypress PSoC Microcontroller |

- PSoC Official Documents

- PSoC official website

- PSoC Designer software for PSoC 1 family

- PSoC Creator software for PSoC 3 / 4 / 5LP families

- PSoC Programmer software for PSoC 1 / 3 / 4 / 5LP families

- ARM Official Documents for PSoC 4 / 5

- Other

- PSoC Developer

- IoT Expert PSoC Tutorials

- Psoc-chile El primer web site en Español sobre Microcontroladore Psoc