LGA 771

LGA 771, also known as Socket J, is a CPU interface introduced by Intel in 2006.[1] It is used in Intel Core microarchitecture and NetBurst microarchitecture(Dempsey) based DP-capable server processors, the Dual-Core Xeon is codenamed Dempsey, Woodcrest, and Wolfdale and the Quad-Core processors Clovertown, Harpertown, and Yorkfield-CL. It is also used for the Core 2 Extreme QX9775.

| |

| Type | LGA |

|---|---|

| Chip form factors | Flip chip land grid array |

| Contacts | 771 |

| FSB frequency | 667 MT/s, 1066 MT/s, 1333 MT/s, 1600 MT/s |

| Voltage range | Varies |

| Processors | Intel Dual-Core Xeon E/X/L 50xx–52xx Intel Quad-Core Xeon X 33xx Intel Quad-Core Xeon E/X/L 53xx–54xx Intel Core 2 Extreme QX9775 |

| Predecessor | Socket 604 |

| Successor | LGA 1366 |

This article is part of the CPU socket series | |

It was succeeded by LGA 1366 for the Nehalem-based Xeon processors.

Technical specifications

.png)

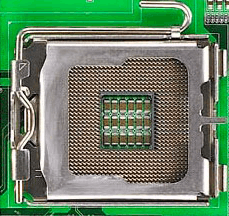

As its name implies, it is a land grid array with 771 contacts. The word "socket" in this instance is a misnomer, as the processor interface has no pin holes. Instead, it has 771 protruding lands which touch contact points on the underside of the microprocessor.

The "J" in "Socket J" refers to the now-canceled processor codenamed "Jayhawk", which was expected to debut alongside this interface. It is intended as a successor to Socket 604 and takes much of its design from LGA 775 and is almost pin compatible with LGA 775. Socket 771 CPUs are rotated 90 degrees and have two pins swapped. Small adapters developed by Chinese computer DIY enthusiasts are available to allow LGA 771 CPUs to be installed in LGA 775 motherboards, if the BIOS microcode supports them (but it is also possible to add supporting microcode manually).

Single core processors

| Name | Cores | Frequency | L2 Cache | TDP | FSB | Release Date | Price |

|---|---|---|---|---|---|---|---|

| Xeon 30XX Series | |||||||

| Xeon L3014 | 1 | 2.40 | 3 MB | 30W | 1066 | Q1 2008 | OEM |

Dual core processors

- Hyperthreading supported only on 50xx series processors(codenamed Dempsey)

| Name | Cores | Frequency | L2 Cache | TDP | FSB | Release date | Price |

|---|---|---|---|---|---|---|---|

| Xeon 50XX series | |||||||

| Xeon 5030 | 2 | 2.66 | 2*2 MB | 95W | 667 | ||

| Xeon 5040 | 2.83 | ||||||

| Xeon 5050 | 3.00 | ||||||

| Xeon 5060 | 3.20 | 130W | 1066 | ||||

| Xeon 5063 | 3.20 | 95W | |||||

| Xeon 5070 | 3.46 | 130W | |||||

| Xeon 5080 | 3.73 | 130W | |||||

| Xeon 31XX Series | |||||||

| Xeon E3113 | 2 | 3.00 | 6 MB | 65W | 1333 | Q3 2008 | OEM |

| Xeon 51XX series | |||||||

| Xeon 5110 | 2 | 1.60 | 4 MB | 65W | 1066 | ||

| Xeon 5120 | 1.86 | 1066 | |||||

| Xeon 5130 | 2.00 | 1333 | Q2 2006 | ||||

| Xeon 5140 | 2.33 | ||||||

| Xeon LV 5148 | 2.33 | 40W | |||||

| Xeon 5150 | 2.66 | 65W | |||||

| Xeon 5160 | 3.00 | 80W | |||||

| Xeon E52XX series | |||||||

| Xeon E5205 | 2 | 1.86 | 6 MB | 65W | 1066 | ||

| Xeon E5220 | 2.33 | 1333 | |||||

| Xeon L52XX series | |||||||

| Xeon L5215 | 2 | 1.86 | 6 MB | 20W | 1066 | ||

| Xeon L5240 | 3.00 | 40W | 1333 | ||||

| Xeon X52XX series | |||||||

| Xeon X5260 | 2 | 3.33 | 6 MB | 80W | 1333 | Q4 2007 | |

| Xeon X5270 | 3.50 | 1333 | Q3 2008 | ||||

| Xeon X5272 | 3.40 | 1600 | Q4 2007 | ||||

Quad core processors

| Name | Cores | Frequency | L2 Cache | TDP | FSB | Release date | Price |

|---|---|---|---|---|---|---|---|

| Xeon X33XX Series | |||||||

| Xeon X3323 | 4 | 2.50 | 6 MB | 80W | 1333 | Q1 2008 | OEM |

| Xeon X3353 | 2.67 | 12 MB | |||||

| Xeon X3363 | 2.83 | ||||||

| Xeon E53XX series | |||||||

| Xeon E5310 | 4 | 1.60 | 8 MB | 80W | 1066 | Q4 2006 | |

| Xeon E5320 | 1.86 | ||||||

| Xeon E5335 | 2.00 | 1333 | Q1 2007 | ||||

| Xeon E5345 | 2.33 | ||||||

| Xeon L53XX series | |||||||

| Xeon L5310 | 4 | 1.60 | 8 MB | 50W | 1066 | Q1 2007 | |

| Xeon L5318 | 1.60 | 40W | |||||

| Xeon L5320 | 1.86 | 50W | |||||

| Xeon L5335 | 2.00 | 50W | 1333 | Q3 2007 | |||

| Xeon X53XX series | |||||||

| Xeon X5355 | 4 | 2.66 | 8 MB | 120W | 1333 | Q4 2006 | |

| Xeon X5365 | 3.00 | 150W | Q3 2007 | ||||

| Xeon E54XX series | |||||||

| Xeon E5405 | 4 | 2.00 | 12 MB | 80W | 1333 | Q4 2007 | |

| Xeon E5410 | 2.33 | ||||||

| Xeon E5420 | 2.50 | ||||||

| Xeon E5430 | 2.66 | ||||||

| Xeon E5440 | 2.83 | Q1 2008 | |||||

| Xeon E5450 | 3.00 | Q4 2007 | |||||

| Xeon E5462 | 2.80 | 1600 | |||||

| Xeon E5472 | 3.00 | 1600 | |||||

| Xeon L54XX series | |||||||

| Xeon L5408[3] | 4 | 2.13 | 12 MB | 40W | 1066 | Q1 2008 | |

| Xeon L5410 | 2.33 | 50W | 1333 | ||||

| Xeon L5420 | 2.50 | ||||||

| Xeon L5430 | 2.66 | Q3 2008 | |||||

| Xeon X54XX series | |||||||

| Xeon X5450 | 4 | 3.00 | 12 MB | 120W | 1333 | Q4 2007 | |

| Xeon X5460 | 3.16 | ||||||

| Xeon X5470 | 3.33 | Q3 2008 | |||||

| Xeon X5472 | 3.00 | 1600 | Q4 2007 | ||||

| Xeon X5482 | 3.20 | 150W | |||||

| Xeon X5492 | 3.40 | Q3 2008 | |||||

| Core 2 Extreme QX97XX series | |||||||

| QX9775 | 4 | 3.20 | 12 MB | 150W | 1600 | Q1 2008 | |

References

- "Intel® Socket Test Technology for LGA771". Intel. Retrieved June 29, 2016.

- "Intel® Xeon® Processor 5140 (4M Cache, 2.33 GHz, 1333 MHz FSB) Specifications". Retrieved July 28, 2016.

- "Intel® Xeon® Processor L5408 (12M Cache, 2.13 GHz, 1066 MHz FSB) Product Specifications". Intel® ARK (Product Specs). Retrieved September 9, 2017.