MOS Technology 8568

The MOS Technology 8568 Video Display Controller (VDC) was the graphics processor responsible for the 80 column or RGBI display on D[CR] models of the Commodore 128 personal computer. In the Commodore 128 service manual, this part was referred to as the "80 column CRT controller." The 8568 embodied many of the features of the older 6545E monochrome CRT controller plus RGBI color.

The original ("flat") Commodore 128 used the 8563 video controller to generate the 80 column display. The 8568 was essentially an updated version of the 8563, combining the latter's functionality with glue logic that had been implemented by discrete components in physical proximity to the 8563. Unlike the 8563, the 8568 included an unused (in the C-128) active low interrupt request line (/INTR), which was asserted when the "ready" bit in the 8568's status register changed from 0 to 1. Reading the control register would automatically deassert /INTR. Owing to differences in pin assignments and circuit interfacing, the 8563 and 8568 are not electrically interchangeable.

The Commodore 128 had two video display modes, which were usually used singularly, but could be used simultaneously if the computer was connected to two compatible video monitors. The VIC-II chip, also found in the Commodore 64, was mapped directly into main memory—the video memory and CPUs (the 8502 and Z80A processors) shared a common 128 KB RAM, and the VIC-II control registers were accessed as memory locations (that is, they were memory mapped).

Unlike the VIC-II, the 8568 had its own local video RAM, 64K in the C-128DCR model (sold in North America) and, depending on the date of manufacture of the particular machine, either 16 or 64K in the C-128D model (marketed in Europe). Addressing the VDC's internal registers and dedicated video memory must be accomplished by indirect means. First the program must tell the VDC which of its 37 internal registers is to be accessed. Next the program must wait until the VDC is ready for the access, after which a read or write on the selected internal register may be performed. The following code is typical of a register read:

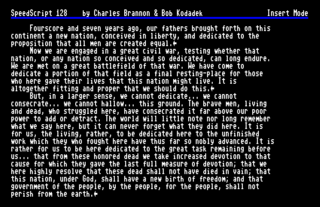

ldx #regnum ;VDC register to access

stx $d600 ;write to control register

loop bit $d600 ;check bit 7 of status register

bpl loop ;VDC not ready

lda $d601 ;read from VDC register

...

The following code is typical of a register write operation:

ldx #regnum ;VDC register to write to

stx $d600 ;write to control register

loop bit $d600 ;check bit 7 of status register

bpl loop ;VDC not ready

sta $d601 ;write to VDC register

...

Owing to this somewhat cumbersome method of controlling the 8568, the maximum possible frame rate in bit-mapped mode is generally too slow for arcade-style action video games, in which bit-intensive manipulation of the display is required.

The final versions of the 8568 had the revision codes R9a or R9b appended to the part number, apparently indicating undocumented improvements.

Features

- 80 × 25 characters text resolution

- 720 × 700 pixels maximum video resolution[1]

- Interlaced up to 80 × 50 text, 640H × 480V bitmap

- 3 character modes: standard, semigraphic and graphic, double width & HiRes bitmap.

- Output: digital RGBI with 16 colors or 16 gray shades, plus limited monochrome composite.

- Features: Interlace mode, horizontal & vertical scrolling, Light pen input, hardware cursor, underline, blink, reverse video, 2 character sets of 256 each, update ready interrupt

- Can access 64 KByte of memory, programmable to interface either 4164/4464 or 4416 DRAM

- 48 pins, +5 Volt DC supply.[2]

Register Listing

This information was adapted from the Commodore 128 Programmer's Reference Guide[3]

| Register | Hexadecimal | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Description |

|---|---|---|---|---|---|---|---|---|---|---|

| Horizontal Total | ||||||||||

| Horizontal Displayed | ||||||||||

| Horizontal Sync Position | ||||||||||

| Vertical/Horizontal Sync Width | ||||||||||

| Vertical Total | ||||||||||

| Vertical Adjust | ||||||||||

| Vertical Displayed | ||||||||||

| Vertical Sync Position | ||||||||||

| Interlace Mode | ||||||||||

| Character Total Vertical | ||||||||||

| Cursor Mode, Cursor Start Scan Line | ||||||||||

| Cursor End Scan Line | ||||||||||

| Display Start Address High Byte | ||||||||||

| Display Start Address Low Byte | ||||||||||

| Cursor Position High Byte | ||||||||||

| Cursor Position Low Byte | ||||||||||

| Light Pen Vertical Position | ||||||||||

| Light Pen Horizontal Position | ||||||||||

| Update Address High Byte | ||||||||||

| Update Address Low Byte | ||||||||||

| Attribute Start Address High Byte | ||||||||||

| Attribute Start Address Low Byte | ||||||||||

| Character Total Horizontal, Character Display Horizontal | ||||||||||

| Character Display Vertical | ||||||||||

| Vertical Smooth Scrolling | ||||||||||

| Horizontal Smooth Scrolling | ||||||||||

| Foreground/Background color | ||||||||||

| Address Increment per Row | ||||||||||

| Character Base Address | ||||||||||

| Underline Scan Line | ||||||||||

| Word Count | ||||||||||

| Data Register | ||||||||||

| Block Start Address High Byte | ||||||||||

| Block Start Address Low Byte | ||||||||||

| Display Enable Begin | ||||||||||

| Display Enable End | ||||||||||

| DRAM Refresh Rate | ||||||||||

| SYNC Polarity (undocumented) |

Notes

- ^ In Commodore 128 terminology, the VIC-II display was called the 40 column display, and the VDC, 80 column, due to the number of columns of fixed-pitch text that could be natively displayed.

- ^ Commodore service manual 314001-08 (1987).

- ^ The 8563/8568 hardware is always visible on the address and data buses regardless of which mode in which the C-128 is operating. Hence it is possible to generate an 80 column display while running in C-64 compatibility mode. There is, of course, no C-64 operating system support.

References

- "empty". Graphic Booster 128

- "empty". Archived from the original on 2009-10-28. 090425 geocities.com

- Commodore Capital, Inc., (1986). Commodore 128 programmer's reference guide. p.294, New York, NY: Bantam Books, Inc.

- "Uncovered: The VDC 8568's 38th register". Archived from the original on 2012-02-19. Retrieved 2008-12-30.