Motorola 6845

The Motorola 6845, or MC6845, was a display controller that was widely used in 8-bit computers during the 1980s. Originally intended for designs based on the Motorola 6800 CPU and given a related part number, it was more widely used alongside various other processors, and was most commonly found in machines based on the Zilog Z80 and MOS 6502.

The 6845 is not an entire display solution on its own; the chip's main function is to properly time access to the display memory, and to calculate the memory address of the next portion to be drawn. Other circuitry in the machine then uses the address provided by the 6845 to fetch the pattern and then draw it. The implementation of that hardware is entirely up to the designer, and varied widely among machines. The 6845 is intended for character displays, but could also be used for pixel-based graphics, with some clever programming.

Among its better-known uses is the BBC Micro, Amstrad CPC, and Videx VideoTerm display cards for the Apple II. It is also part of many early graphics adapter cards for the IBM PC, including the MDA, Hercules Graphics Card (HGC), and Color Graphics Adapter (CGA). Its functionality was duplicated and extended by custom circuits in the EGA and VGA PC video adapters.

Originally designed by Hitachi as the HD46505, Hitachi-built versions are in a wide variety of Japanese computers, from Sony, Sharp, Panasonic, and Casio. It is also known as the 6845 CRTC or the CRTC6845, meaning "cathode ray tube controller".

A common clone of this CRT controller is the United Microelectronics Corporation (UMC) UM6845E CRT controller.

Overview

The chip generates the signals necessary to interface with a raster display but does not generate the actual pixels, though it does contribute cursor and video-blanking information to the pixel video (intensity) signals. It is used to produce correctly timed horizontal and vertical sync and provide the address in memory from which the next pixel or set of pixels should be read. The process of reading that value, converting it into pixels, and sending it to a CRT is left to other circuits. Because of this, systems using the 6845 may have very different numbers and values of colors, or may not support color at all.

Interlaced and non-interlaced output modes are supported, as is a hardware text cursor. The sync generation includes generation of horizontal and vertical video blanking signals, which are used to condition the external pixel generation circuits. Also, an internal latch is provided which when triggered will duplicate and retain a copy of the video address so that it can later be read back by the CPU. This is useful for light pens and light guns which can function by sending a pulse to the 6845 when the electron beam passes, allowing a running program to read back the location that was pointed at. Because of this feature, most computer video adapters using a 6845 included a light pen interface, though it was usually an internal connector on the board itself, not on the outside of the computer, and it was usually undocumented in the user manual.

Because all aspects of video timing are programmable, a single machine can switch between NTSC and PAL timings in software. The 6845 can be used to drive monitors or any other raster display.

Internals

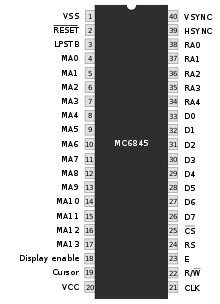

The chip has a total of 18 8-bit registers controlling all aspects of video timings. Only two addresses are exposed to external components - one to select which internal register is to be read or written to and another to access that register.

The 6845 is intended for character based displays. Every address it generates is composed of two parts - a 14 bit character address and a 5 bit row address. Using the full address range RA0-RA4:CA0-CA13 the 6845 can address 214+5 = 512 kibi-words of memory, where a word may be any number of bits chosen by the system designer as the memory width. If the word size is one byte, as is often the case, the 6845 can address 512 KiB. If the word size is 32 bits, e.g. for 32-bit color graphics with one pixel per word, then the 6845 can address 2048 kiB, which equals 2 MiB (and for 64-bit words, it can address twice that). These limits arise from the combination of the 6845 and the design of the external memory connected to it, not from the 6845 alone. The number of unique addresses that the 6845 can address is limited (to 512*1024), but the amount of memory that the 6845 can address is theoretically unlimited, because the 6845 imposes no limit on the size of each memory location that it addresses.

It is also significant that each word addressed by the 6845 does not have to equal one pixel or one character. As an example, consider the use of the 6845 in the IBM CGA, where the word size is one byte and each word represents four or eight pixels (in the medium- or high- resolution graphics mode, respectively) or one-half character. In CGA alphanumeric (text) mode, there are two bytes per character, accessed sequentially by the 6845—the first byte is a character code byte and the second byte is a character attribute byte.

The character address increases linearly. When the chip signals horizontal sync it increases the row address. If the row address does not equal the programmatically set number of rows per character, then the character address is reset to the value it had at the beginning of the scanline that was just completed. Otherwise the row address is reset to zero and the memory address continues increasing linearly. This causes the same sequence of character values to be re-read from the memory for each raster line of each character row, before the 6845 advances the memory address to the next character row and repeats the same pattern. Therefore, if a character occupies one "word" in the video buffer, a display of l lines and c columns of characters with s scan lines per character requires l × c words of memory to represent a full screen of characters but takes s times that many memory accesses to complete one refresh cycle (as each line of character words is repeatedly read s times before the next one is read). This means that character displays using the 6845, compared to all-points-addressable graphics displays of the same resolution, require much less memory but still require high memory bandwidth on the order of the bandwidth required for graphics. (A different video display controller that buffers one whole line of character data internally can avoid this repeated reading of each line of characters from the display buffer RAM, reducing the required memory bandwidth and allowing either slower, less expensive memory chips to be used, more time for a system CPU to access the memory, or a combination of both.

In the 1970s, 1980s, and to a lesser extent the 1990s, memory was expensive, fast memory was especially so, and this was an important concern. In the 1970s and early to mid-1980s, chip circuit densities were not very high either, and putting an 80-byte or larger character buffer into a chip like the 6845 might have enlarged the chip die by 50-100%, in turn making it more expensive by a few times that factor due to the exponential growth of chip defect rates and the consequent decline of production yield with die size. Therefore, adding such a character buffer to the 6845 was not a cost-effective approach when the chip was introduced. Now that memory is very inexpensive, fast memory included, there is little motivation to reduce the memory bandwidth required by a video display controller, so this is no longer an important engineering consideration. At the same time, chip densities have skyrocketed—which is actually the main reason for today's low memory prices—and many chips used in computers have large buffers and caches; a chip like the 6845 designed today could easily use a character line cache to avoid reading and re-reading characters for each video scan line within a character line. For low-power handheld devices, which would be the main ones likely to use character displays now, the power used for high-bandwidth memory access would be good reason to reduce the memory bandwidth for display refresh through the use of a line cache in the display controller.

If the character address is used to look up a character reference in RAM and the row address to index a table of character graphics in ROM an ordinary text mode display is constructed. The character reference read from memory must be combined with the row address to form the address for the character graphics ROM, with the character reference selecting a set of scan line patterns that forms one character and the row address indexing into that set to select one scan line. In other words, the ROM address is split into two parts in order to use the ROM as a two-dimensional array: the first dimension selects a character, and the second selects a row of that character's graphic pattern.

Linear framebuffers

As described above, the 6845 is not ordinarily able to provide large linear framebuffers. A design could use only the 14 bit character address and set the number of rows per character to 1 but it would be constrained to 16 kB of addressable memory.

A solution is found in the Amstrad CPC, which combines the row address and character address to provide linear scanlines within a non-linear buffer. It maps row address RA0-RA2 to memory address MA11-MA13 and character address CA0-CA10 to memory address MA0-MA10. This has the advantages of easier programming for non-character display and easy smooth horizontal scrolling but can impede smooth vertical scrolling.

Differences from the 6545

Although overwhelmingly compatible, a number of small variations exist between the 6845 and 6545.

The biggest difference is that the 6545 may be configured so that it has sole access to the address bus for video memory. Two additional registers are included for setting any address the CPU wishes to read and the chip alternates between outputting addresses for display generation and the display set for CPU access.

Smaller changes are that the MOS Technology and one variation of the Rockwell 6545 lack interlaced output support and all 6545s include an optional address skew, which delays display enable for one character cycle if set. This second feature was incorporated into later variations of the Motorola 6845.

The 6545 may be set to work in linear 14 bit mode using a status bit. On the 6845 the same thing requires adjustment of the character height.

Tricks

The 6845 reads the start address for its display once per frame. However, if the internal timing values on the chip are altered at the correct time it can be made to prepare for a new frame without ending the current one - creating a non-continuous break in generated addresses midway through the display. This is commonly used by demos and much more rarely games to provide one moving area of the display (usually the play field) and one static (usually a status display).

Vertical scrolling appears constrained because only the character start address can be set and the row address is always zeroed at frame start, but by adjusting border times it is possible to shift the position the framebuffer is shown on the raster display for increments in between whole characters. With drawing of blank pixels at the screen edges, this can be made invisible to the user creating just the illusion of a smooth vertical scroll.

See also

- Motorola 6847, a complete video display generator

- List of home computers by video hardware