35

16

I wanted to know how to find L2 cache size in Linux...

for L1 cache size, I am doing the following

pico /proc/cpuinfo

what about L2 cache size?

35

16

I wanted to know how to find L2 cache size in Linux...

for L1 cache size, I am doing the following

pico /proc/cpuinfo

what about L2 cache size?

30

cat /sys/devices/system/cpu/cpu0/cache/index2/size

or check dmidecode

or use lshw

27

EDIT 3: Heh, sorry, just do sudo dmidecode -t cache and it will show you your CPU's cache information. To tell what section you are looking at (L1 or L2), look at the Configuration: line. You want Configuration: Enabled, Not Socketed, Level 2.

17

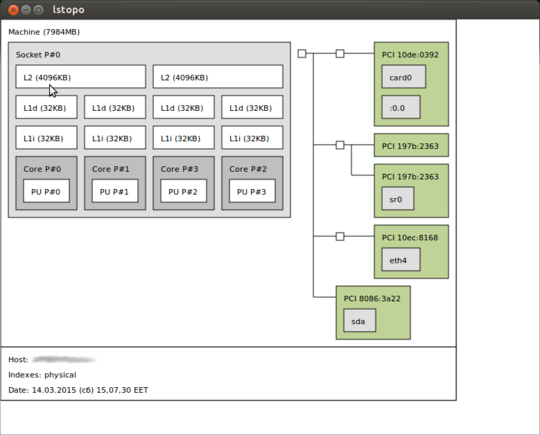

You should check the following tool. It gives the most accurate information from all the tools I've tried. This is the command line version output:

~$ lstopo-no-graphics

Machine (7984MB)

Socket L#0

L2 L#0 (4096KB)

L1d L#0 (32KB) + L1i L#0 (32KB) + Core L#0 + PU L#0 (P#0)

L1d L#1 (32KB) + L1i L#1 (32KB) + Core L#1 + PU L#1 (P#1)

L2 L#1 (4096KB)

L1d L#2 (32KB) + L1i L#2 (32KB) + Core L#2 + PU L#2 (P#2)

L1d L#3 (32KB) + L1i L#3 (32KB) + Core L#3 + PU L#3 (P#3)

And this is the graphical interface:

11

Just use: lscpu

Sample output:

$ lscpu

Architecture: x86_64

CPU op-mode(s): 32-bit, 64-bit

Byte Order: Little Endian

CPU(s): 4

On-line CPU(s) list: 0-3

Thread(s) per core: 1

Core(s) per socket: 4

Socket(s): 1

NUMA node(s): 1

Vendor ID: GenuineIntel

CPU family: 6

Model: 42

Stepping: 7

CPU MHz: 3401.000

BogoMIPS: 6784.57

Virtualization: VT-x

L1d cache: 32K

L1i cache: 32K

L2 cache: 256K

L3 cache: 8192K

NUMA node0 CPU(s): 0-3

6

getconf

getconf -a | grep CACHE

gives:

LEVEL1_ICACHE_SIZE 32768

LEVEL1_ICACHE_ASSOC 8

LEVEL1_ICACHE_LINESIZE 64

LEVEL1_DCACHE_SIZE 32768

LEVEL1_DCACHE_ASSOC 8

LEVEL1_DCACHE_LINESIZE 64

LEVEL2_CACHE_SIZE 262144

LEVEL2_CACHE_ASSOC 8

LEVEL2_CACHE_LINESIZE 64

LEVEL3_CACHE_SIZE 20971520

LEVEL3_CACHE_ASSOC 20

LEVEL3_CACHE_LINESIZE 64

LEVEL4_CACHE_SIZE 0

LEVEL4_CACHE_ASSOC 0

LEVEL4_CACHE_LINESIZE 0

Or for a single level:

getconf LEVEL2_CACHE_SIZE

The cool thing about this interface is that it is just a wrapper around the POSIX sysconf C function (cache arguments are non-POSIX extensions), and so it can be used from C code as well.

Tested in Ubuntu 16.04.

x86 CPUID instruction

The CPUID x86 instruction also offers cache information, and can be directly accessed by userland: https://en.wikipedia.org/wiki/CPUID

glibc seems to use that method for x86. I haven't confirmed by step debugging / instruction tracing, but the source for 2.28 sysdeps/x86/cacheinfo.c does that:

__cpuid (2, eax, ebx, ecx, edx);

TODO create a minimal C example, lazy now, asked at: https://stackoverflow.com/questions/14283171/how-to-receive-l1-l2-l3-cache-size-using-cpuid-instruction-in-x86

ARM also has an architecture-defined mechanism to find cache sizes through registers such as the Cache Size ID Register (CCSIDR), see the ARMv8 Programmers' Manual 11.6 "Cache discovery" for an overview.

4

dmesg | grep cache will show your L1 and L2 related information.

Or dmesg (or dmesg.boot) and search for the CPU model. Then google on that. – Hennes – 2012-11-19T00:26:06.863

lscpuis not accurate on some CPUs with exotic configuration. For example the CPU from my answer gives the following (omitted some info): CPU family: 6 Model: 15 Stepping: 11 CPU MHz: 1866.742 BogoMIPS: 3733.48 Virtualization: VT-x L1d cache: 32K L1i cache: 32K L2 cache: 4096K NUMA node0 CPU(s): 0-3 The CPU is Xeon L5320 with 8MB L2 total. – zloster – 2016-02-27T20:57:31.040