ARM is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings. It was named the Advanced RISC Machine and, before that, the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit instruction set architecture in numbers produced.

Introduction

ARM is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings. It was named the Advanced RISC Machine and, before that, the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit instruction set architecture in numbers produced.The ARM architecture is generally described as a Reduced Instruction Set Computer (RISC) architecture, as it incorporates these typical RISC architecture features:

- A uniform register file load/store architecture, where data-processing operates only on register contents, not directly on memory contents.

- Simple addressing modes, with all load/store addresses determined from register contents and instruction fields only.

CPU modes

The ARM architecture specifies the following CPU modes. At any moment in time, the CPU can be in only one mode, but it can switch modes due to external events (interrupts) or programmatically. User mode The only non-privileged mode. System mode The only privileged mode that is not entered by an exception. It can only be entered by executing an instruction that explicitly writes to the mode bits of the CPSR.- Supervisor (svc) mode A privileged mode entered whenever the CPU is reset or when a SWI instruction is executed.

- Abort mode A privileged mode that is entered whenever a prefetch abort or data abort exception occurs.

- Undefined mode A privileged mode that is entered whenever an undefined instruction exception occurs.

- Interrupt mode A privileged mode that is entered whenever the processor accepts an IRQ interrupt.

- Fast Interrupt mode A privileged mode that is entered whenever the processor accepts an FIQ interrupt.

64 bit support

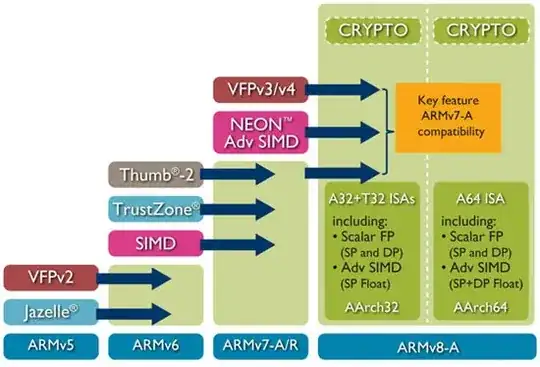

Released in late 2011, ARMv8 represents the first fundamental change to the ARM architecture. It adds a 64-bit architecture, dubbed 'AArch64', and a new 'A64' instruction set. Within the context of ARMv8, the 32-bit architecture and instruction set are referred to as 'AArch32' and 'A32', respectively. The Thumb instruction sets are referred to as 'T32' and have no 64-bit counterpart. ARMv8 allows 32-bit applications to be executed in a 64-bit OS, and for a 32-bit OS to be under the control of a 64-bit hypervisor.As of March 2012, only the ARMv8-A ("application") profile has been defined, and no implementations have been announced.

To both AArch32 and AArch64, ARMv8 makes VFP and advanced SIMD (NEON) standard. It also adds cryptography instructions supporting AES and SHA-1/SHA-256.

AArch64 features:

- New instruction set, A64

- 31 general-purpose 64-bit registers

- Instructions are still 32 bits long and mostly the same as A32

- Most instructions can take 32-bit or 64-bit arguments

- Addresses assumed to be 64-bit

- A new exception system

- Fewer banked registers and modes

- Memory translation from 48-bit virtual addresses based on the existing LPAE, which was designed to be easily extended to 64-bit

Sources: arm.com and wikipedia