23

2

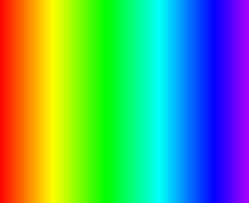

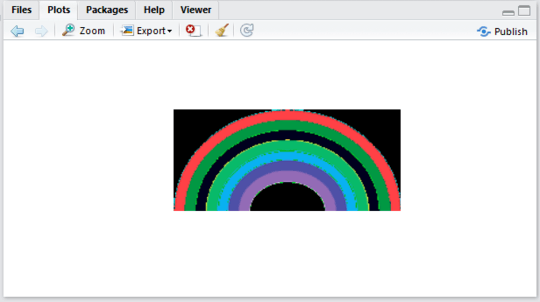

You would simply take this image and make every color added one to every hexadecimal digit. For example, #49de5f would become #5aef60 (with the 9 looping to an a, and the f looping to a 0.)

This would also mean that all white (#ffffff) would become black (#000000) because all f loops back to 0, but all black will become a lighter shade of black (#111111).

Scoring is based on the least number of bytes used, as this is a code-golf question.

Use the below image as the input image for your code, and put the output image of your code into your answer.

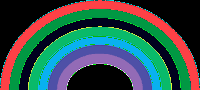

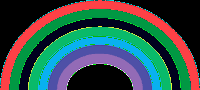

If you want to, you can also use this other rainbow image:

What assumptions can we make on input/output format, if we would like to use a programming language designed for hardware/FPGA design? – Reinstate Monica - ζ-- – 2016-06-19T15:52:09.120

@hexafraction I think by default you can take as a file or as hex code iirc. – Rɪᴋᴇʀ – 2016-06-19T16:03:13.220

@hexafraction http://meta.codegolf.stackexchange.com/q/9093/8478

– Martin Ender – 2016-06-19T16:03:37.480@MartinEnder Thanks. I'm still a bit unclear in regard to output timing due to the nature of Verilog as an HDL; should I pop into the site chat to seek further clarification? – Reinstate Monica - ζ-- – 2016-06-19T16:09:03.560

@hexafraction Either that or ask on meta. – Martin Ender – 2016-06-19T17:43:32.160

5@Peanut, it would be good to have a test case which includes

efbytes (which should becomef0as opposed to00which happens when you just add 17 and take mod 256). – Martin Ender – 2016-06-19T17:44:40.6332You should post an image for sample output, rather than just providing sample input. Other than that, this is a very nice first post! Welcome to the site! – James – 2016-06-19T18:59:03.437