Nanoelectromechanical relay

A nanoelectromechanical (NEM) relay is an electrically actuated switch that is built on the nanometer scale using semiconductor fabrication techniques. They are designed to operate in replacement, or in conjunction, with traditional semiconductor logic. While the mechanical nature of NEM relays makes them switch much slower than solid-state relays, they have many advantageous properties, such as zero current leakage and low power consumption, which make them potentially useful in next generation computing.

A typical NEM Relay requires a potential on the order of the tens of volts in order to "pull in" and have contact resistances on the order of gigaohms. Coating contact surfaces with platinum can reduce achievable contact resistance to as low as 3 kΩ.[1] Compared to transistors, NEM relays switch relatively slowly, on the order of nanoseconds.[2]

Operation

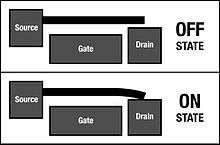

A NEM relay can be fabricated in two, three, or four terminal configurations. A three terminal relay is composed of a source (input), drain (output), and a gate (actuation terminal). Attached to the source is a cantilevered beam that can be bent into contact with the drain in order to make an electrical connection. When a significant voltage differential is applied between the beam and gate, and the electrostatic force overcomes the elastic force of the beam enough to bend it into contact with the drain, the device "pulls in" and forms an electrical connection. In the off position, the source and drain are separated by an air gap. This physical separation allows NEM relays to have zero current leakage, and very sharp on/off transitions.[3]

The nonlinear nature of the electric field, and adhesion between the beam and drain cause the device to "pull out" and lose connection at a lower voltage than the voltage at which it pulls in. This hysteresis effect means there is a voltage between the pull in voltage, and the pull out voltage that will not change the state of the relay, no matter what its initial state is. This property is very useful in applications where information needs to be stored in the circuit, such as in static random-access memory.[1]

Fabrication

NEM relays are usually fabricated using surface micromachining techniques typical of microelectromechanical systems (MEMS).[4] Laterally actuated relays are constructed by first depositing two or more layers of material on a silicon wafer. The upper structural layer is photolithographically patterned in order to form isolated blocks of the uppermost material. The layer below is then selectively etched away, leaving thin structures, such as the relay's beam, cantilevered above the wafer, and free to bend laterally.[1] A common set of materials used in this process is polysilicon as the upper structural layer, and silicon dioxide as the sacrificial lower layer.

NEM relays can be fabricated using a back end of line compatible process, allowing them to be built on top of CMOS.[1] This property allows NEM relays to be used to significantly reduce the area of certain circuits. For example, a CMOS-NEM relay hybrid inverter occupies 0.03 µm2, one-third the area of a 45 nm CMOS inverter.[5]

History

The first switch made using silicon micro-machining techniques was fabricated in 1978.[6] Those switches were made using bulk micromachining processes and electroplating.[7] In the 1980s, surface micromachining techniques were developed[8] and the technology was applied to the fabrication of switches, allowing for smaller, more efficient relays.[9]

A major early application of MEMS relays was for switching radio frequency signals at which solid-state relays had poor performance.[10] The switching time for these early relays was above 1 µs. By shrinking dimensions below one micrometer,[11] and moving into the nano scale, MEMS switches have achieved switching times in the ranges of hundreds of nanoseconds.[5]

Applications

Mechanical computing

Due to transistor leakage, there is a limit to the theoretical efficiency of CMOS logic. This efficiency barrier ultimately prevents continued increases in computing power in power-constrained applications.[12] While NEM relays have significant switching delays, their small size and fast switching speed when compared to other relays means that mechanical computing utilizing NEM Relays could prove a viable replacement for typical CMOS based integrated circuits, and break this CMOS efficiency barrier.[3][2]

A NEM relay switches mechanically about 1000 times slower than a solid-state transistor takes to switch electrically. While this makes using NEM relays for computing a significant challenge, their low resistance would allow many NEM relays to be chained together and switch all at once, performing a single large calculation.[2] On the other hand, transistor logic has to be implemented in small cycles of calculations, because their high resistance does not allow many transistors to be chained together while maintaining signal integrity. Therefore, it would be possible to create a mechanical computer using NEM relays that operates at a much lower clock speed than CMOS logic, but performs larger, more complex calculations during each cycle. This would allow a NEM relay based logic to perform to standards comparable to current CMOS logic.[2]

There are many applications, such as in the automotive, aerospace, or geothermal exploration businesses, in which it would be beneficial to have a microcontroller that could operate at very high temperatures. However, at high temperatures, semiconductors used in typical microcontrollers begin to fail as the electrical properties of the materials they are made of degrade, and the transistors no longer function. NEM relays do not rely on the electrical properties of materials to actuate, so a mechanical computer utilizing NEM relays would be able to operate in such conditions. NEM relays have been successfully tested at up to 500 °C, but could theoretically withstand much higher temperatures.[13]

Field-programmable gate arrays

The zero leakage current, low energy usage, and ability to be layered on top of CMOS properties of NEM relays make them a promising candidate for usage as routing switches in Field-programmable gate arrays (FPGA). A FPGA utilizing a NEM relay to replace each routing switch and its corresponding static random-access memory block could allow for a significant reduction in programming delay, power leakage, and chip area compared to a typical 22nm CMOS based FPGA.[14] This area reduction mainly comes from the fact that the NEM relay routing layer can be built on top of the CMOS layer of the FPGA.

References

- Parsa, Roozbeh; Lee, W. Scott; Shavezipur, Mohammad; Provine, J; Mitra, Subhashish; Wong, H.-S. Philip; Howe, Roger T. (7 March 2013). "Laterally Actuated Platinum-Coated Polysilicon NEM Relays". Journal of Microelectromechanical Systems. 22 (3): 768–778. doi:10.1109/JMEMS.2013.2244779.

- Chen, Fred; Kam, Hei; Markovic, Dejan; Liu, Tsu-Jae King; Stojanovic, Vladimir; Alon, Elad (2008-11-10). "Integrated Circuit Design with NEM Relays". ICCAD '08 Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design. pp. 750–757. ISBN 9781424428205. Retrieved 29 October 2014.

- Chen, F; Spencer, M; Nathanael, R; ChengCheng, Wang; Fariborzi, H; Gupta, A; Hei, Kam; Pott, V; Kaeseok, Jeon; Tsu-Jae, King Liu; Markovic, D.; Stojanovic, V.; Alon, E. (February 2010). "Demonstration of integrated micro-electro-mechanical switch circuits for VLSI applications". 2010 IEEE International Solid-State Circuits Conference - (ISSCC). pp. 150–151. CiteSeerX 10.1.1.460.2411. doi:10.1109/ISSCC.2010.5434010. ISBN 978-1-4244-6033-5.

- Kam, Hei; Pott, V; Nathanael, R; Jeon, Jaeseok; Alon, E; Liu, Tsu-Jae King (December 2009). "Design and reliability of a micro-relay technology for zero-standby-power digital logic applications". 2009 IEEE International Electron Devices Meeting (IEDM). pp. 1–4. doi:10.1109/IEDM.2009.5424218. ISBN 978-1-4244-5639-0.

- Akarvardar, K; Elata, D; Parsa, R; Wan, G. C.; Yoo, K; Provine, J; Peumans, P; Howe, R.T.; Wong, H.-S.P. (10 December 2007). "Design Considerations for Complementary Nanoelectromechanical Logic Gates". 2007 IEEE International Electron Devices Meeting. pp. 299–302. doi:10.1109/IEDM.2007.4418930. ISBN 978-1-4244-1507-6.

- Petersen, Kurt (October 1978). "Dynamic Micromechanics on Silicon: Techniques and Devices". IEEE Transactions on Electron Devices. 25 (10): 1241–1250. Bibcode:1978ITED...25.1241P. doi:10.1109/T-ED.1978.19259.

- Petersen, Kurt (May 1982). "Silicon as a mechanical material". Proceedings of the IEEE. 70 (5): 420–457. Bibcode:1982IEEEP..70..420P. doi:10.1109/PROC.1982.12331.

- Bustillo, J.M.; Howe, R.T.; Muller, R.S. (August 1998). "Surface micromachining for microelectromechanical systems". Proceedings of the IEEE. 86 (8): 1552–1574. CiteSeerX 10.1.1.120.4059. doi:10.1109/5.704260.

- Sakata, M (February 1989). "An electrostatic microactuator for electro-mechanical relay". An Investigation of Micro Structures, Sensors, Actuators, Machines and Robots. IEEE Micro Electro Mechanical Systems, Proceedings. pp. 149–151. doi:10.1109/MEMSYS.1989.77980.

- Yao, J.J.; Chang, M.F. (June 1995). "A Surface Micromachined Miniature Switch for Telecommunications Applications with Signal Frequencies from DC up to 4 GHZ". Proceedings of the International Solid-State Sensors and Actuators Conference - TRANSDUCERS '95. 2. pp. 384–387. doi:10.1109/SENSOR.1995.721827.

- Jang, Weon Wi; Lee, Jeong Oen; Yoon, Jun-Bo; Kim, Min-Sang; Lee, Ji-Myoung; Kim, Sung-Min; Cho, Keun-Hwi; Kim, Dong-Won; Park, Donggun; Lee, Won-Seong (March 2008). "Fabrication and characterization of a nanoelectromechanical switch with 15-nm-thick suspension air gap". Applied Physics Letters. 92 (10): 103110–103110–3. Bibcode:2008ApPhL..92j3110J. doi:10.1063/1.2892659.

- Calhoun, Benton, H.; Wang, Alice; Chandrakasan, Anantha (September 2005). "Modeling and Sizing for Minimum Energy Operation in Subthreshold Circuits" (PDF). IEEE Journal of Solid-State Circuits. 40 (9): 1778. Bibcode:2005IJSSC..40.1778C. doi:10.1109/JSSC.2005.852162. Retrieved 29 October 2014.

- Lee, Te-Hao; Bhunia, Swarup; Mehregany, Mehran (10 September 2010). "Electromechanical Computing at 500°C with Silicon Carbide". Science. 329 (5997): 1316–1318. Bibcode:2010Sci...329.1316L. doi:10.1126/science.1192511. PMID 20829479.

- Chen, Chen; Parsa, Roozbeh; Patil, Nishant; Chong, Soogine; Akarvardar, Kerem; Provine, J; Lewis, David; Watt, Jeff; Howe, Roger T.; Wong, H.-S. Philip; Mitra, Subhashish (2010-02-21). "Efficient FPGAs using nanoelectromechanical relays". Proceedings of the 18th annual ACM/SIGDA international symposium on Field programmable gate arrays - FPGA '10. pp. 273–282. doi:10.1145/1723112.1723158. ISBN 9781605589114.