C-element

The Muller C-element (C-gate, hysteresis flip-flop, or sometimes coincident flip-flop, two-hand safety circuit) is a small digital block widely used in design of asynchronous circuits and systems. It has been specified formally in 1955 by David E. Muller[9] and first used in ILLIAC II computer.[10] In terms of the theory of lattices, the C-element is a semimodular distributive circuit, whose operation in time is described by a Hasse diagram.[11][12][13] The C-element is closely related to the rendezvous[14] and join[15] elements, where an input is not allowed to change twice in succession. In some cases, when relations between delays are known, the C-element can be realized as a sum-of-product (SOP) circuit [16],[17]. Earlier techniques for implementing the C-element[18][19] include Schmidt trigger,[20] Eccles-Jordan flip-flop and last moving point flip-flop.

Truth table and delay assumptions

For two input signals the C-element is defined by the equation , which corresponds to the following truth table:

| 0 | 0 | 0 |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 | 1 |

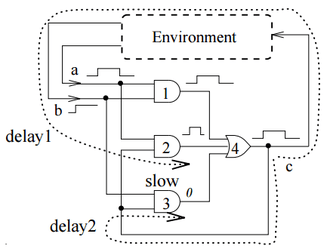

This table can be turned into a circuit using the Karnaugh map. However, the obtained implementation is naive, since nothing is said about delay assumptions. To understand under what conditions the obtained circuit is workable, it is necessary to do additional analysis, which reveals that

- delay1 is a propagation delay from node 1 via environment to node 3,

- delay2 is a propagation delay from node 1 via internal feedback to node 3,

- delay1 must be greater than delay2.

Thus, the naive implementation is correct only for slow environment.[21] The definition of C-element can be easily generalized for multiple-valued logic or even for continuous signals:

For example, the truth table for a balanced ternary C-element with two inputs is

| −1 | −1 | −1 |

| −1 | 0 | |

| −1 | 1 | |

| 0 | −1 | |

| 0 | 0 | 0 |

| 0 | 1 | |

| 1 | −1 | |

| 1 | 0 | |

| 1 | 1 | 1 |

Implementations of the C-element

Depending on the requirements to the switching speed and power consumption, the C-element can be realized as a coarse- or fine-grain circuit. Also, one should distinguish between single-output and differential[22] realizations of C-element. Differential realization is possible using only NANDs (only NORs). A single-output realization is workable if and only if:[23]

- The circuit, where each input of a C-element is connected through a separate inverter to its output, is semimodular relatively to the state, where all the inverters are excited.

- This state is live for the output gate of C-element.

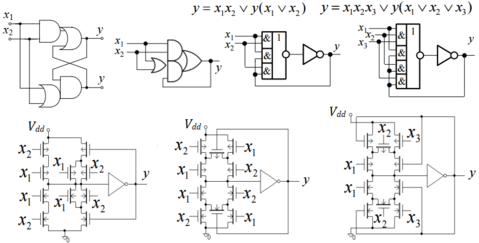

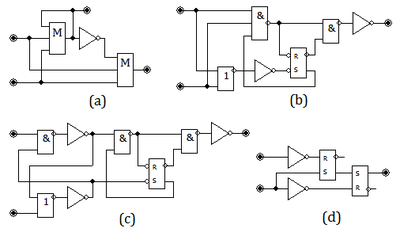

Gate-level implementations

There is a number of different single-output circuits of C-element built on logic gates[24][25]. In particular, the so-called Maevsky's implementation[26][27][28] is a non-distributive circuit loosely based on[29]. Non-distributivity is introduced sometimes to increase concurrency. The 3NAND gate in this circuit can be replaced by two 2NAND gates. The C-element using only two-input gates has been proposed by Tsirlin[30] and then synthesized by Starodoubtsev et al. using Taxogram language [31] This circuit coincides with that attributed (without reference) to Bartky [26] and can operate without the input latch. Yet another version of the C-element built on two RS latches has been synthesized by Murphy[32] using Petrify tool. However, this circuit includes inverter connected to one if the inputs. This inverter should have small delay. However, there are realizations of RS latches that already have one inverted input, for example [33]. Some speed-independent approaches [34][35] assume that zero-delay input inverters are available on all gates, which is a violation of true speed-independence but is fairly safe in practice. Other examples of using this assumption also exist.[36]

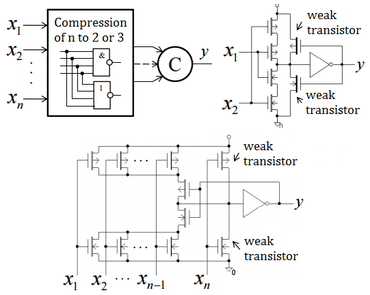

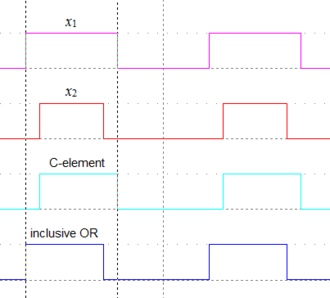

Static and semistatic implementations

In his report[9] Muller proposed to realize C-element as a majority gate with feedback. However, to avoid hazards linked with skews of internal delays, the majority gate must have as small number of transistors as possible.[37][38] Generally, C-elements with different timing assumptions[39] can be built on AND-OR-Invert (AOI)[40][41] or its dual, OR-AND-Invert (OAI) gate[42][43] and inverter. Yet another option patented by Varshavsky et al.[44] [45] is to shunt the input signals when they are not equal each other. Being very simple, these realizations dissipate more power due to the short-circuits. Connecting an additional majority gate to the inverted output of C-element, we obtain inclusive OR (EDLINCOR) function:[46][47] . Some simple asynchronous circuits like pulse distributors[48] can be built solely on majority gates.

Semistatic C-element stores its previous state using two cross-coupled inverters, similar to an SRAM cell. One of the inverters is weaker than the rest of the circuit, so it can be overpowered by the pull-up and pull-down networks. If both inputs are 0, then the pull-up network changes the latch's state, and the C-element outputs a 0. If both inputs are 1, then the pull-down network changes the latch's state, making the C-element output a 1. Otherwise, the input of the latch is not connected to either or ground, and so the weak inverter dominates and the latch outputs its previous state. There are also versions of semistatic C-element built on devices with negative differential resistance (NDR).[49][50] NDR is usually defined for small signal, so it is difficult to expect that such a C-element will operate in full range of voltages or currents.

Generalizations and non-transistor implementations

Since the majority gate is a particular case of threshold gate, any of known realizations of threshold gate[51] can in principle be used for building a C-element. In the multiple-valued case, however, connecting the output of majority gate to one or several inputs may have no desirable effect. For example, using the ternary majority function defined as[52]

does not lead to the ternary C-element specified by the truth table, if the sum is not split into pairs. However, even without such a splitting two ternary majority functions are suitable for building a ternary inclusive OR gate. Both the Maevsky and Tsirlin circuits are based actually on so-called David cell.[53] Its fast transistor-level implementation is used in the semistatic C-element proposed.[54] Yet another semistatic circuit using pass transistors (actually MUX 2:1) has been proposed.[55] Other technologies suitable for realizing asynchronous primitives including C-element, are: carbon nanotubes, single-electron tunneling devices[56], quantum dots[57], and molecular nanotechnology[58].

References

- I. E. Sutherland, "Micropipelines", Communications of the ACM, vol. 32, no. 6, pp. 720–738, 1989.

- C. H. van Berkel, "Beware the isochronic fork", Report UR 003/91, Philips Research Laboratories, 1991.

- V. B. Marakhovsky, Logic design of asynchronous circuits. Slides on the course. CS&SE Department, SPbPU.

- V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky, B. S. Tsirlin, "H flip-flop", USSR author's certificate SU1562964, Jul. 5, 1990.

- V. I. Varshavsky, "β-driven threshold elements", IEEE Great Lakes Symposium on VLSI 1998, pp. 52–58.

- V. I. Varshavsky, "Threshold element and method of designing the same," Patent US6338157, Jan. 8, 2002.

- Y. A. Stepchenkov, Y. G. Dyachenko, A. N. Denisov, Y. P. Fomin, "H flip-flop", Patent RU2371842, Oct. 27, 2009.

- A. Bystrov, A. Yakovlev, Asynchronous circuit synthesis by direct mapping: Interfacing to environment. Technical Report, CS Department, University of Newcastle upon Tyne, October 2001.

- D. E. Muller, Theory of asynchronous circuits. Report no. 66, Digital Computer Laboratory, University of Illinois at Urbana-Champaign, 1955.

- H. C. Breadley, "ILLIAC II — A short description and annotated bibliography", IEEE Transactions on Electronic Computers, vol. EC-14, no. 3, pp. 399–403, 1965.

- D. E. Muller and W. S. Bartky, "A theory of asynchronous circuits", Int. Symposium on the Switching Theory in Harvard University, pp. 204–243, 1959.

- W. J. Poppelbaum, Introduction to the Theory of Digital Machines. Math., E.E. 294 Lecture Notes, University of Illinois at Urbana-Champaign.

- J. Gunawardena, "A generalized event structure for the Muller unfolding of a safe net", Int. Conference on Concurrency Theory (CONCUR) 1993, pp. 278–292.

- M. J. Stucki, S. M. Ornstein, W. A. Clark, "Logical design of macromodules", in Proceedings of AFIPS 1967, pp. 357–364.

- J. C. Ebergen, J. Segers, I. Benko, "Parallel Program and Asynchronous Circuit Design", Workshops in Computing, pp. 50–103, 1995.

- P.A. Beerel, J.R. Burch and T.H. Meng,"Checking combinational equivalence of speed-independent circuits," Formal Methods in System Design, vol. 13, no. 1, pp. 37-85, 1998.

- H. Park, A. He, M. Roncken and X. Song, "Semi-modular delay model revisited in context of relative timing", IET Electronics Letters, vol. 51, no. 4, pp. 332–334, 2015.

- Technical Progress Report, Jan. 1959, University of Illinois at Urbana-Champaign.

- W . J. Poppellbaum, N. E. Wiseman, "Circuit design for the new Illinois computer", Report no. 90, University of Illinois at Urbana-Champaign, 1959.

- N. P. Singh, A design methodology for self-timed systems. MSc thesis, MIT, 1981, 98 p.

- J. Cortadella, M. Kishinevsky, Tutorial: Synthesis of control circuits from STG specifications. Summer school, Lyngby, 1997.

- A. Mokhov, V. Khomenko, D. Sokolov and A. Yakovlev, "On dual-rail control logic for enhanced circuit robustness", IEEE Int. Conference on Application of Concurrency to System Design (ACSD) 2012, pp. 112–121.

- B. S. Tsirlin, "A Survey of Equivalent Problems of Realizing Circuits in the AND-NOT Basis that are Speed-Independent", Soviet Journal of Computer and Systems Sciences, vol. 24, 1986, pp. 58–69 (Б. С. Цирлин, "Обзор эквивалентных проблем реализации схем в базисе И-НЕ, не зависящих от скорости", Изв. АН СССР, Техническая кибернетика, №2, 1986, с. 159–171).

- B. S. Tsirlin, "H flip-flop", USSR author's certificate SU1096759, Jun. 7, 1984.

- B. S. Tsirlin, "Multiple input H flip-flop", USSR author's certificate SU1162019, Jun. 15, 1985.

- M. Kuwako, T. Nanya, "Timing-reliability evaluation of asynchronous circuits based on different delay models", IEEE International Symposium on Advanced Research in Asynchronous Circuits and Systems (ASYNC) 1994, pp. 22–31.

- J. A. Brzozowski, K. Raahemifar, "Testing C-elements is not elementary", Working Conference on Asynchronous Design Methodologies (ASYNC) 1995, pp. 150–159.

- P. A. Beerel, J. R. Burch, T. H. Meng, "Checking combinational equivalence of speed-independent circuits", Formal Methods in System Design, vol. 13, no. 1, 1998, pp. 37–85.

- V. I. Varshavsky, O. V. Maevsky, Yu. V. Mamrukov, B. S. Tsirlin, "H flip-flop", USSR author's certificate SU1081801, Mar. 23, 1984.

- B. S. Tsirlin, "H-flip-flop", USSR author's certificate SU1324106, Jul. 15, 1987.

- N. A. Starodoubtsev, S. A. Bystrov, "Monotonic behavior refinement for synthesis of two-input-gate asynchronous circuits", IEEE Int. Midwest Symposium on Circuits and Systems (MWSCAS) 2004, vol. I, pp. I-521–524.

- J. P. Murphy, "Design of latch-based C-element", Electronics Letters, vol. 48, no. 19, 2012, pp. 1190–1191.

- V. A. Maksimov and Ya. Ya. Petrichkovich "RS flip-flop," USSR author's certificate SU1164867, Jun. 30, 1985.

- P. Beerel and T. H.-Y. Meng. "Automatic gate-level synthesis of speed-independent circuits", IEEE/ACM Int. Conference on Computer-Aided Design (ICCAD) 1992, pp. 581–587.

- A. Kondratyev, M. Kishinevsky, B. Lin, P. Vanbekbergen, and A. Yakovlev, "Basic gate implementation of speed-independent circuits", ACM Design Automation Conference (DAC) 1994, pp. 56–62.

- A. V. Yakovlev, A. M. Koelmans, A. Semenov, D. J. Kinniment, "Modelling, analysis and synthesis of asynchronous control circuits using Petri nets", Integration, the VLSI Journal, vol. 21, no. 3, pp. 143—170, 1996.

- D. Hampel, K. Prost, and N. Scheingberg, "Threshold logic using complementary MOS device", Patent US3900742, Aug. 19, 1975.

- D. Doman, Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive Silicon Archived 2015-10-08 at the Wayback Machine. Wiley, 2012, 327 p.

- K. S. Stevens, R. Ginosar and S. Rotem, "Relative timing [asynchronous design]", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 11, no. 1, pp. 129–140, 2003.

- H. Zemanek, "Sequentielle asynchrone Logik", Elektronische Rechenanlagen, vol. 4, no. 6, pp. 248–253, 1962. Also available in Russian as Г. Цеманек, "Последовательная асинхронная логика", Mеждународный симпозиум ИФАК Теория конечных и вероятностных автоматов 1962, с. 232—245.

- W. Fleischhammer, "Improvements in or relating to asynchronous bistable trigger circuits", UK patent specification GB1199698, Jul. 22, 1970.

- T.-Y. Wuu and S. B. K. Vrudhula, "A design of a fast and area efficient multi-input Muller C-element", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 1, no. 2, pp. 215–219, 1993.

- H. K. O. Berge, A. Hasanbegovic, S. Aunet, "Muller C-elements based on minority-3 functions for ultra low voltage supplies", IEEE Int. Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS) 2011, pp. 195–200.

- V. I. Varshavsky, A. Y. Kondratyev, N. M. Kravchenko, and B. S. Tsirlin, "H flip-flop", USSR Author's certificate SU1411934 Jul. 23, 1988.

- V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky and B. S. Tsirlin, "H flip-flop", USSR Author's certificate SU1443137, Dec. 7, 1988.

- D. A. Pucknell, "Event-driven logic (EDL) approach to digital systems representation and related design processes", IEE Proceedings E, Computers and Digital Techniques, vol. 140, no. 2, pp. 119—126, 1993.

- A. Yakovlev, M. Kishinevsky, A. Kondratyev, L. Lavagno, M. Pietkiewicz-Koutny, "On the models for asynchronous circuit behaviour with OR causality", Formal Methods in System Design, vol. 9, no. 3, pp. 189—233. 1996.

- J. C. Nelson, Speed-independent counting circuits. Report no. 71, Digital Computer Laboratory, University of Illinois at Urbana-Champaign, 1956.

- C.-H. Lin, K. Yang, A. F. Gonzalez, J. R. East, P. Mazumder, G. I. Haddad, "InP-based high speed digital logic gates using an RTD/HBT heterostructure", Int. Conference on Indium Phosphide and Related Materials (IPRM) 1999, pp. 419–422.

- P. Glosekotter, C. Pacha, K. F. Goser, W. Prost, S. Kim, H. van Husen, et al., "Asynchronous circuit design based on the RTBT monostable-bistable logic transition element (MOBILE)", Symposium Integrated Circuits and Systems Design 2002, pp. 365–370.

- V. Beiu, J. M. Quintana, M. J. Avedillo, "VLSI implementations of threshold logic – A comprehensive survey", IEEE Transactions on Neural Networks, vol. 14, no. 5, pp. 1217–1243, 2003.

- V. Varshavsky, B. Ovsievich, "Networks composed of ternary majority elements", IEEE Transactions on Electronic Computers, vol. EC-14, no. 5, pp. 730–733, 1965.

- M. Courvoisier and P. Azema, "Asynchronous sequential machines with request/acknowledge operating mode," IEE Electronics Letters, Vol. 10, no. 1, pp.8-10, 1974.

- S. M. Fairbanks, "Two-stage Muller C-element", United States Patent US6281707, Aug. 28, 2001.

- A. Morgenshtein, M. Moreinis, R. Ginosar, "Asynchronous gate-diffusion-input (GDI) circuits", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 8, pp. 847–856, 2004.

- S. Safiruddin, S. D. Cotofana, "Building blocks for delay-insensitive circuits using single electron tunneling devices", IEEE Conference on Nanotechnology 2007, pp. 704–708.

- V. I. Varshavsky, "Logic design and quantum challenge", Int. Workshop on Physics and Computer Modeling of Devices Based on Low-Dimensional Structures 1995, pp. 134–146.

- A. J. Martin, P. Prakash, "Asynchronous nano-electronics: Preliminary investigation" Archived 2016-03-04 at the Wayback Machine, IEEE Int. Symposium on Asynchronous Circuits and Systems (ASYNC) 2008, pp. 58–68.