-1

From the book Modern Operating systems;

The abundance of transistors on a single chip is leading to a problem: what to do with all of them?

We saw one approach above: superscalar architectures, with multiple functional units. But as the number of transistors increases, even more is possible. One obvious thing to do is put bigger caches on the CPU chip. That is definitely hap- pening, but eventually the point of diminishing returns will be reached.

The obvious next step is to replicate not only the functional units, but also some of the control logic. The Intel Pentium 4 introduced this property, called multithreading or hyperthreading (Intel’s name for it), to the x86 processor, and several other CPU chips also have it—including the SPARC, the Power5, the Intel Xeon, and the Intel Core family. To a first approximation, what it does is allow the CPU to hold the state of two different threads and then switch back and forth on a nanosecond time scale. (A thread is a kind of lightweight process, which, in turn, is a running program; we will get into the details in Chap. 2.)

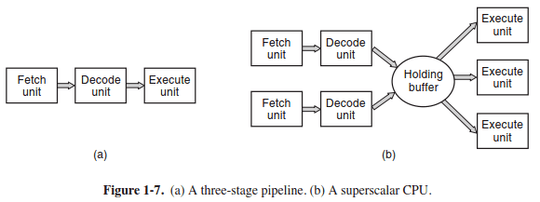

A superscalar architecture is given in a previous figure 1-7(b):

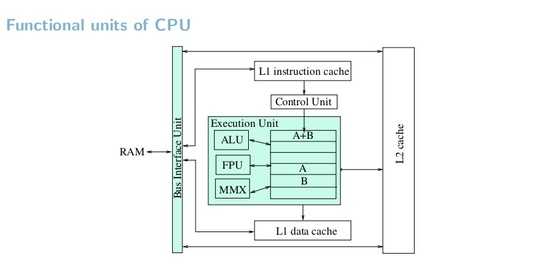

I wonder what a functional unit and a control logic in a cpu mean?

Does a superscalar architecture also replicate control logic?

Are "functional unit" and "Execute unit" the same thing?

Is "control logic" the same as "Fetch unit" and "Decode unit"?

I am hesitant to answer yes to the above questions because of the following reasons. The text says superscalar architectures replicate the functional units, while multithreading replicates not only the functional units, but also the control logic.

But in figure 1.7(b), the superscalar one have multiple fetch and decode units besides multiple execute units, so I am not sure if "control logic == fetch and decode units" and "functional unit == execute unit".

Also by multithreading, the text actually means time-multiplex. I don't know how replicating control logic is necessary for time-multiplex? Can't multiple threads or processes share the same control units (fetch unit and decode unit) at different times?

1Doesn't the book define "functional unit"? If it doesn't find a better book. – DavidPostill – 2015-01-12T17:34:49.987

no it doesn't. can you tell me what they are? – Tim – 2015-01-12T17:42:51.727