3

1

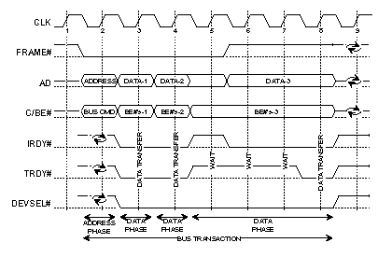

According to this article , the bus is the circuit that connects the motherboard . The faster the speed of the bus , the quicker data can be transferred . Bus speed is measured in MHz (Mega Hertz) and a bus speed of 66 MHZ means that that are 66 million cycles per second . Hertz means how the frequency of x every second

For CPU , 66 MHz means 66 million instructions can be processed every second

How about for Bus ?? How much data is terms of btyes is transferred for every cycle ??

"For CPU , 66 MHz means 66 million instructions can be processed every second" -- That's an incorrect assumption, more than one instruction can be performed per clock cycle. As for your question, the size of the bus matters. IE: a 32-bit data bus can move less data at once than a 64-bit data bus could. – Ƭᴇcʜιᴇ007 – 2014-03-12T17:48:21.830

When it comes to frequency considerations, there are other factors to be considered... Such as bus widths. Simply, a pin can change state 66 million times in a second at (66 MHz). – Ghassan – 2014-03-12T17:51:20.920

For the amount of data (in bytes) being sent, it depends on how big the bus is (in bits). If you have a 32-bit bus, you can send 4 Bytes of information per cycle (8 bits / 1 byte). – None – 2014-03-12T17:52:54.047

1

To continue on what @techie007 said, it is not limited to more than one CPU instuction per cycle. DDR Memory will do two data transfers per one clock cycle.

– Scott Chamberlain – 2014-03-12T18:22:55.403