On older systems with a real bus, it works like Ethernet in the old days when all computers were connected physically to the same wire or medium--or the new days with wireless Ethernet--all systems on the same wire listen and receive all traffic. This would include RAM on that bus.

Similarly, all devices/chips on a given bus receive all traffic, but are only supposed to act on data meant for them. There's various schemes to make RAM only respond when it's addressed (Commodore 64 used a device called a PLA, other systems used other chips or 74LS chips) Chip level or bus level protocols are needed and used to make sure multiple devices don't talk at once; and they have to be followed--"collisions" on busses can cause the CPU to freeze or behave erratically (it's a device on the bus too).

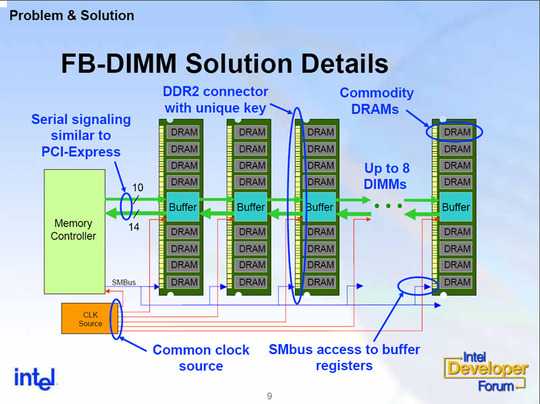

RAM on modern CPUs is directly connected to specific pins on the CPU and is no longer on a bus (a 1-device bus is called a port). Modern hardware in general is moving away from a shared medium model. PCIe works more like switched Ethernet, SATA is point-to-point, and USB and other things go through controllers that are on PCIe.

PCI stands for Peripheral Component Interconnect--and that's a better name for the mechanism--interconnect--than bus these days. Again RAM is on its own ports.

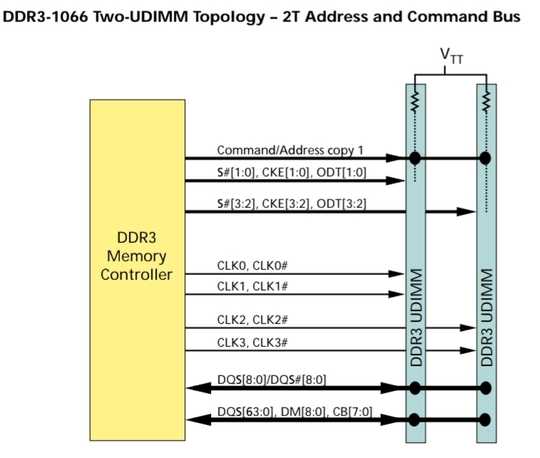

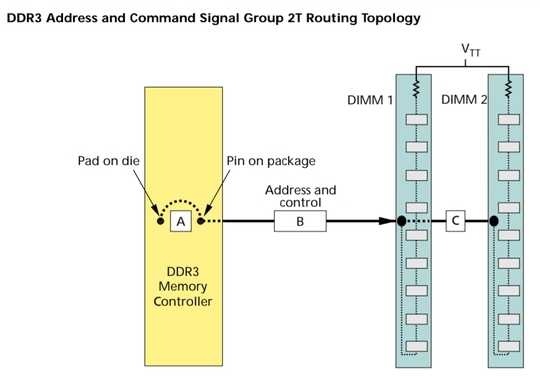

But say I have 2 DIMMS in a computer and each DIMM has 6 chips (or whatever number). And I try to access some address, does each of the 12 chips see a voltage change? – user1140098 – 2020-02-15T02:36:34.247