1

Every electronics engeneer knows that connecting more chips on the same line increases its capasistence and, thus, degrades the frequency. So, memory speed must be dependent on the number of chips in the channel. How in this case the DDR memory manufacturers manage to label their devices as DDR3-1333 MHz for instance without this information? Is there a limit of chips per channel or one module per channel is assumed?

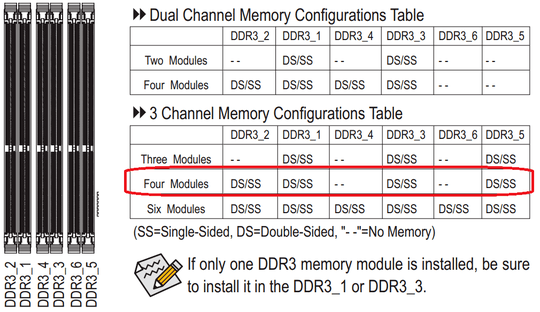

Apart from that, what if there is capacity imbalance in multicahhel architecture? Here is a recommendation from my MB manufacturer, X58A-UD3R, to use 4 modules for 3-channel mode

Can I have 4GB+2GB+2GB (assuming the timings are identical)? What are performance Implications? The Intel controller says that interleaving mode is needed to make gain of 3 channels. What will happen to the interleaving when there is such capacity imbalance?

Can I have 4GB+2GB+2GB (assuming the timings are identical)? What are performance Implications? The Intel controller says that interleaving mode is needed to make gain of 3 channels. What will happen to the interleaving when there is such capacity imbalance?

What if modules of different timings are combined? Should I choose the worst common denominator?

In other words, I want to know what are DIMM specifications depending on the environment? How are the DIMM specifications related with the environment it is supposed to work?

Originally posted in http://www.tomshardware.co.uk/answers/id-1651405/miltiple-sticks-single-channel.html

The label on a memory module is simply the maximum speed at which it is capable of operating. It is not a guarantee that it will operate at that speed in any particular system. – Dave Tweed – 2013-04-14T14:16:13.750

thanks, this is interesting but incomplete. I want to know more exactly: how the maximum speed is affected when I combine memories? – Val – 2013-04-14T14:41:36.320

That depends on your memory controller and the number of memory ranks on the DIMM(s). In the case of most regular PCs (with ranks 2 DIMMs) max speed does decrease when you add a second pair (or in the case of Nehalens or some Xeons, a a second triplet/second quad) of DIMMs. – Hennes – 2013-04-14T16:07:53.893

@Hennes, how is it possible? The DIMM sticks are it the same position as the controller. They must drive more capacity when connected to the other DIMM chips. How do you know that it is controller dependent? Why SDRAM standard prescirbes the RAM chips to support other chips in the channel but SDRAM controller may violate this requirement? How do I know which category my controller belongs? – Val – 2013-04-14T16:25:39.567

Some MB manufacturers will actually list memory modules that have been tested to work with that motherboard. So no guessing is needed by the end-user. – sawdust – 2013-04-14T22:27:01.813

@sawdust: Yes, they listed. But why should I constrain myself to those? Ok, I throw away the sticks I have already installed for various reasons and constrain myself to your choice. What then? What is the answer now, provided I will use only those modules? You say it is simple. Please answer. – Val – 2013-04-15T10:08:53.837

I am not sure I understand it well enough to explain it clearly. Searching on memory ranks and reading posts on ServerFault however does suggest that adding more ranks adds more capacity (the electrical kind, not the sum of RAM).

However I can not seem to find any sites which clearly explain memory ranks. Some (like http://csinfo.cna.nl.ca/jrussell/hwarefun/Mem_ranks_ENG.pdf ) give limited information, but most do not go in depth.

[Continued because

too long by 99 characters]I only got mildly curious because the maximum speed for my desktops memory went down when I added more memory to it (previously 3x2GB at 133MHz, later 3x2GB+3x4GB at 1066MHz). I expected the command timing to go to 2T, but not the drop from 667 to 533. – Hennes – 2013-04-19T13:02:03.247

533 is a limit for 1066 memories. The fact that your controller operates at the speed of slower memory confirms that MIXING DIFFERENT TIMING MEMORIES DID NOT DEGRADE the performance, despite you claim the opposite. It does not matter that you had faster memories before. The fact is that adding faster memories does not degrade the frequency. It also says that capacitive load does not have any negative impact. Also, I see that you are not going to argue for your statement that combining modules may degrade frequency because of the controller (and not because memories load each other). – Val – 2013-04-19T16:47:28.550